2011 IEEE Radio Frequency Integrated Circuits Symposium Baltimore, Maryland 5-7 June 2011

# PROGRAM

# **Baltimore Convention Center**

Sponsored by IEEE Microwave Theory and Techniques Society IEEE Electron Device Society and The IEEE Solid-State Circuits Society

#### **RFIC Plenary and Reception Sunday Evening (5 June 2011)**

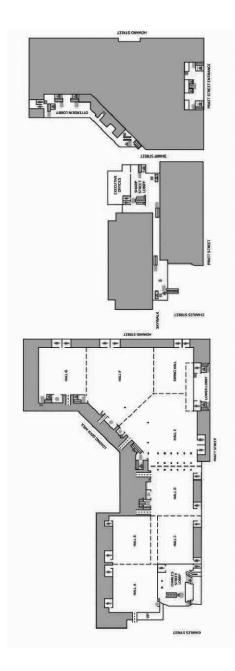

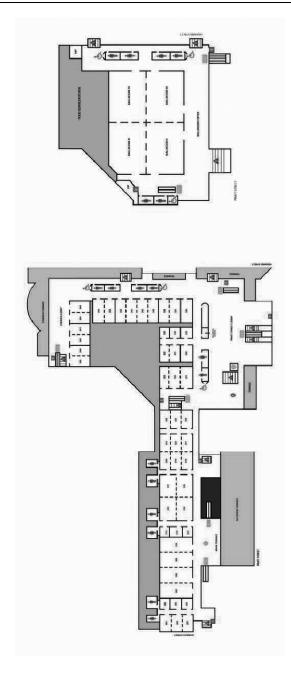

After a busy day of excellent RFIC Workshops (see page 64-80) the Plenary Session and RFIC Reception will be held in Sunday evening – 5 June 2011. The Plenary Session starts at 5:40PM in the Baltimore Convention Center (BCC), Level 400, Ballroom III-IV. The Plenary Session will include two outstanding speakers (see pages 8-9), RFIC Service Recognition and Student Paper Awards ceremony. Immediately following the RFIC Plenary Session is the famous RFIC Reception in the adjacent Ballroom I-II. This social event is a key component of the RFIC Symposium, providing the opportunity to connect with old friends, make new acquaintances, and catch up on latest news in the wireless industry. Admittance is included with RFIC Symposium registration. Additional tickets can also be purchased separately at registration. The RFIC Reception is sponsored by the RFIC Steering Committee, our Platinum (RFMD) and Gold (Skyworks) sponsors.

#### RFIC Week Activities (5-7 June 2011)

#### Saturday, 4 June 2011

2:00 PM - 6:00 PM

Registration - BCC

#### Sunday, 5 June 2011

7:00 AM - 6:00 PM 7:00 AM - 8:00 AM 8:00 AM - 5:20 PM 5:40 PM - 7:00 PM 7:00 PM - 9:00 PM

#### Monday, 6 June 2011

6:30 AM - 8:30 AM 7:00 AM - 9:00 AM 7:00 AM - 5:00 PM 8:00 AM - 9:40 AM 10:00 AM - 11:40 AM Noon - 1:20 PM 2:20 PM - 3:40 PM 4:00 PM - 5:20 PM

#### Tuesday, 7 June 2011

6:30 AM - 8:30 AM 7:00 AM - 9:00 AM 7:00 AM - 5:00 PM 8:00 AM - 9:40 AM 10:00 AM - 11:40 AM Noon - 1:20 PM Noon - 2:00PM Registration - BCC Workshop Breakfast – BCC, Level 300, Foyer Workshops and Tutorials - BCC RFIC Plenary – BCC, Level 400, Ballroom III-IV RFIC Reception - BCC, Level 400, Ballroom I-II

Speakers Breakfast – BCC, Level 400, Ballroom I-IV Attendee Breakfast – BCC, Level 300, Foyer Registration – BCC RMO1A RMO1B RMO1C RMO1D RMO2A RMO2B RMO2C RMO2D RFIC Panel and Lunch - BCC, 307-308 RMO3A RMO3B RMO3C RMO3D RMO4A RMO4B RMO4C RMO4D

Speakers Breakfast – BCC, Level 400, Ballroom I-IV Attendee Breakfast – BCC, Level 300, Foyer Registration – BCC RTU1A RTU1B RTU1C RTU2A RTU2B RTU2C RFIC Panel and Lunch - BCC, 307-308 RTUIF – BCC, Hall A

This Program can be found on the RFIC website http://www.rfic2011.org. IMS sessions and exhibits are held on Tuesday - Thursday. IMS program can be found on the IMS website www.ims2011.org.

# **TABLE OF CONTENTS**

The RFIC Symposium will be held in Baltimore, Maryland at the Baltimore Convention Center (BCC) on 5-7 June 2011 in conjunction with the International Microwave Symposium. It opens Microwave week 2011, the largest RF/Microwave meeting of the year.

The RFIC Symposium brings focus to the technical accomplishments in RF Systems, circuit device, and packaging technologies for mobile phones, wireless communication systems, broadband access modems, radar systems and intelligent transport systems.

| Table of Contents                                                      | p. 1   |

|------------------------------------------------------------------------|--------|

| Welcome Message from Chairpersons                                      | p. 2-3 |

| Steering Committee                                                     | p. 4   |

| Advisory Board                                                         | p. 4   |

| Executive Committee                                                    |        |

| Technical Program Committee                                            | p. 5   |

| RFIC Schedule 2011                                                     | p. 6   |

| Plenary Session                                                        | p. 7-9 |

| Session: RMO1A: Wireless Data Transceiver Architectures and Techniques | p. 10  |

| Session: RMO1B: Digital to RF and Sigma-Delta Transmit Modulators      | p. 12  |

| Session: RMO1C: mm-Wave Communication Systems                          | p. 14  |

| Session: RMO1D: Frequency Synthesis: 60GHz and Beyond                  | p. 16  |

| Session: RMO2A: WiMedia UWB and IR-UWB Receivers and Transmitters      | p. 18  |

| Session: RMO2B: Cellular RF                                            | p. 20  |

| Session: RMO2C: Advanced Architecture PA's                             | p. 22  |

| Session: RMO2D: Emerging RFIC Device Technologies                      | p. 24  |

| Session: RMO3A: Low Power Wireless Sensor Techniques                   | p. 26  |

| Session: RMO3B: Low Power LNA Design Techniques                        | p. 28  |

| Session: RMO3C: Devices and circuits for silicon based mm-Wave ICs     | p. 30  |

| Session: RMO3D: mm-Wave VCOs                                           | p. 32  |

| Session: RMO4A: RF characterization and modeling of advanced CMOS      | p. 34  |

| Session: RMO4B: Integrated Front-End RFIC - LNA, Mixers, Filters       | p. 36  |

| Session: RMO4C: High performance CMOS Power Amplifiers                 | p. 38  |

| Session: RMO4D: Frequency Synthesis: Mixed Signal Techniques           | p. 40  |

| Session: RTU1A: mm-Wave modeling of parasitic and passives             | p. 42  |

| Session: RTU1B: Broadband and Low-Noise Amplifiers                     | p. 44  |

| Session: RTU1C: mm-Wave Imagers                                        | p. 46  |

| Session: RTU2A: Wideband Receivers and Building Blocks                 |        |

| Session: RTU2B: Wide Tuning Range Oscillators                          |        |

| Session: RTU2C: mm-Wave Power Amplifiers                               |        |

| Session: RTUIF: RFIC Interactive Forum                                 |        |

| Panel Sessions                                                         |        |

| Workshops and Short Courses                                            |        |

| Registration Information                                               |        |

| US Visa Information                                                    | p. 87  |

| Social Events                                                          |        |

| Guest Programs                                                         |        |

| BCC Floor Plans                                                        | p. 94  |

#### Welcome Message from Chairpersons

On behalf of the Steering Committee, We would like to welcome you to the 2011 IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, which will take place in Baltimore, Maryland 5-7 June, 2011. Our Symposium, held in conjunction with the IEEE MTT-S International Microwave Symposium, opens Microwave Week 2011, the largest world-wide RF/Microwave meeting of the year.

The 2011 RFIC Symposium continues to build upon its heritage as one of the foremost IEEE technical conferences, increasing each year its impact and reputation of excellence. By bringing focus to the technical accomplishments in RF circuits, systems, and devices, the RFIC Symposium has become essential to both the academic and the industrial communities. This year's exciting technical program will showcase the latest innovations in RF integrated circuit design with sessions that cover a broad spectrum of topics from cellular and wireless-connectivity system ICs, broadband wireless communications, digitally enhanced RF circuits, silicon millimeter-wave ICs, and RF device technology, modeling, and characterization. Applications highlighted by the technology include mobile phones, wireless communication systems, broadband access modems, radar systems and intelligent transport systems.

Running in conjunction with the International Microwave Symposium and Exhibit, the RFIC Symposium adds to the excitement of the Microwave Week with three days focused exclusively on RFIC technology and innovation.

The 2011 RFIC Symposium will start on Sunday with half-day and full-day workshops covering a wide array of topics. Some of the topics include: New Architectures for Digitized Receivers, RFIC for Bio-Medical Applications, Imaging at mm-wave and beyond, Cognitive Radios and Spectrum Sensing, Advancements in Linear Power Amplifiers, Efficiency Enhancement Techniques for Power Amplifiers and Transmitters, Advancements and Challenges Toward Radio-in-package and Radioon-chip, Re-configurability Requirements for Multi-standard, Low-Power Operation, and EMI compliant product design practices.

The conference also includes a Plenary Session, which is held on Sunday evening. Keynote addresses will be given by two renowned leaders from in the wireless industry. Both of them will share their views and insights on the direction and challenges that the RF IC design community is facing. The first speaker is the Chief Technical Officer and Co-Founder of Telegent Systems, Dr. Samuel Sheng, who will discuss **"RF Coexistence - Challenges and Opportunities"**. The second speaker is Mr. Ron Ruebusch, Vice President of R&D of Wireless Semiconductor Division of Avago Technologies. He will discuss **"3G to 4G Transition – Challenges and Opportunities"**. In addition to the keynote addresses, the conference holds a student paper competition to encourage the publication of innovative research from university students. Consequently, best student paper awards are presented in the Plenary Session to acknowledge these contributions. The highly anticipated RFIC Reception will follow immediately after the Plenary Session, providing a relaxing time for all to mingle with old friends and catch up on the latest news.

On Monday and Tuesday, the conference will feature lunch-time panel sessions that traditionally draw strong debate between panel members as well as stimulating interaction between attendees and panelists. The Monday panel session is entitled *"Software Defined"*

**Radios** – **Facts and Fantasies**" while the Tuesday panel session is entitled "**What is the limit of multi-radio integration... or rather, is it 'disintegration'?**" Be sure to attend these lively and entertaining forums.

Technical papers will be presented during oral sessions throughout Monday and Tuesday. There will be a total of 129 papers presented in 23 technical focused sessions. On Tuesday's afternoon, our interactive Forum (RTUIF) will feature 31 poster papers and give our attendee a chance to speak directly with authors regarding their work.

The RFIC organization is thankful to the IMS2011 team's strong support for making this conference successful. Most of all, we are particularly thankful to all the technical contributors to the RFIC Symposium. We look forward to your participation. Please continue to make this conference so vibrant within the wireless industry!

We look forward to seeing you in Baltimore!

David Ngo General Chairman

Albert Jerng TPC Chairman

Chris Rudell TPC Co-Chairman

## **Steering Committee**

David Ngo, RFMD, Inc., General Chairman Albert Jerng, Ralink Technology, TPC Chairman Jacques C. Rudell, Univ. of Washington, TPC Co-Chairman Bertan Bakkaloglu, Arizona State Univ., *Finance Chairman* Brian Floyd, North Carolina State Univ., Workshops Chairman Albert Wang, UC Riverside, Workshops Co-Chairman Kevin Kobavashi, RFMD, Inc., Publications Chairman Kevin McCarthy, University College Cork, Publicity Chairman Larry Kushner, Intersil Corp., Panel Sessions Chairman Georg Boeck, TU Berlin, Transactions/Guest Editor Yuhua Cheng, SHRIME Peking Univ., Student Papers Chairman Freek van Straten, NXP Semiconductors, Secretary Noriharu Suematsu, Tohoku Univ., Asia Pacific Liaisons Jenshan Lin, Univ. of Florida, Submission Website Administrator Takao Inoue, Univ. of Texas, Austin, Website Chairman Tina Quach, Consultant, *Conference Manager*

## **Advisory Board**

Natalino Camilleri • Fazal Ali • Reynold Kagiwada • Sayfe Kiaei David Lovelace • Joseph Staudinger • Stefan Heinen

# **Executive Committee**

Yann Deval • Luciano Boglione • Jenshan Lin • David Ngo

## **RFIC 2011 Technical Program Committee**

Ali Afsahi, Broadcom Corp. Fazal Ali, Qualcomm Walid Ali-Ahmad, MediaTek Inc. Bertan Bakkaloglu, Arizona State University Jean-Baptiste Begueret, University of Bordeaux, IMS Lab Didier Belot, ST Microelectronics Paul Blount, Custom MMIC Design Georg Boeck, Berlin Institute of Technology Luciano Boglione, University of Massachusetts Lowell Pierre Busson. ST Microelectronics Natalino Camilleri, Alien Technology Sudipto Chakraborty, Texas Instruments Glenn Chang, MaxLinear Jing-Hong Chen, Analog Devices Nick Cheng, Skyworks Solutions Yuhua Cheng, Shrime Peking University Guang-Kaai Dehng, Mediatek, Inc. Yann Deval, University of Bordeaux Oren Eliezer, XtendWave Brian Floyd, North Carolina State University Eric Fogleman, MaxLinear Ranjit Gharpurey, University of Texas, Austin Aditya Gupta, Northrop Grumman Timothy Hancock, MIT Lincoln Lab Andre Hanke, Infineon Technologies AG Hossein Hashemi, USC Gary Hau, Anadigics Stefan Heinen, RWTH Aachen University Mona Hella, Rensellaer Polytechnic Institute Frank Henkel, IMST GmbH Chun-Ming Hsu, IBM Tian-Wei Huang, National Taiwan University Gernot Hueber, Infineon Technologies Nobuyuki Itoh, Okayama Prefectural University Waleed Khalil, Obio State University Jaber Khoja, Zoran Sayfe Kiaei, ASU, Connection One Bumman Kim, POSTECH Eric Klumperink, University of Twente Kevin Kobayashi, RFMD, Inc. Larry Kushner, Intersil Corp. Youngwoo Kwon, Seoul National University Chang-Ho Lee, Samsung

Fred Lee. SiTime Tzung-Yin Lee, Skyworks Solutions Domine Leenaerts, NXP Semiconductors Donald Y.C. Lie, Texas Tech. University Fujiang Lin, University of Science and Technology of China Jenshan Lin, University of Florida Li Lin. Marvell Semiconductor Ting-Ping Liu, Nuvoton Technology David Lovelace, ON Semiconductor Danilo Manstretta, University of Pavia Kevin McCarthy, University College Cork Srenik Mehta, Atheros Communications Jyoti Mondal, Northrop Grumman Kenjiro Nishikawa, Kagoshima University Sule Ozev, Arizona State University Stefano Pellerano, Intel Corporation Tina Quach, Consultant Sanjay Raman, Virginia Tech Madhukar Reddy, MaxLinear Bill Redman-White, NXP Semiconductors Eli Reese, TriQuint Semiconductor Mark Ruberto, Intel Corporation Francis Rotella, Peregrine Semiconductor Carlos Saavedra, Queen's University, Canada Derek Shaeffer, InvenSense, Inc. Osama Shana'a, MediaTek, Inc. Eddie Spears, RFMD, Inc. Robert Staszewski, Delft University of Technology Joseph Staudinger, Freescale Semiconductor Inc. Bob Stengel, Motorola Labs Freek van Straten. NXP Semiconductors Noriharu Suematsu, Tohoku University Julian Tham, Broadcom Bruce Thompson, Consultant Mark Tiebout, Infineon Technologies Leon Van den Oever, Radio Semiconductor Corporation Jeffrey Walling, Rutgers University Albert Wang, University of California, Riverside Haolu Xie, Fujitsu Microelectronics Li-Wu Yang, Shanghai Jiao-Tong University Patrick Yue, University of California, Santa Barbara Gary Zhang, Skyworks Solutions Herbert Zirath, Chalmers University

# **RFIC Schedule 2011**

The RFIC Symposium will be held in Baltimore, MD in the Baltimore Convention Center (BCC). The headquarters hotels are the Hyatt Regency Baltimore and Hilton Baltimore Convention Center Hotel which are adjacent to the BCC. The RFIC Plenary and Reception will be held on Sunday, 5 June 2011 starting at 5:40 PM.

The RFIC Symposium is held as part of Microwave week. It is followed by the IMS Symposium and Exhibition and by ARFTG. Attendees of RFIC are invited to attend the IMS Plenary Session which will be held on Tuesday's Evening, 7 June 2011.

#### Saturday, 4 June 2011

| 2:00 PM - 6:00 PM | Registration - ACC |

|-------------------|--------------------|

|                   |                    |

#### Sunday, 5 June 2011

| 6:30 AM – 8:30 AM | Speakers Breakfast – BCC, Level 400, Ballroom I-II |

|-------------------|----------------------------------------------------|

| 7:00 AM - 8:00 AM | Workshop Breakfast – BCC, Level 300, Foyer         |

| 7:00 AM - 6:00 PM | Registration - BCC                                 |

| 8:00 AM - 5:20 PM | Workshops and Tutorials - BCC                      |

| 5:40 PM - 7:00 PM | RFIC Plenary – BCC, Level 400, Ballroom III-IV     |

| 7:00 PM - 9:00 PM | RFIC Reception - BCC, Level 400, Ballroom I-II     |

#### Monday, 6 June 2011

| 6:30 AM - 8:30 AM   | Speakers Breakfast – BCC, Level 400, Ballroom I-IV   |

|---------------------|------------------------------------------------------|

| 7:00 AM - 9:00 AM   | Attendee Breakfast – BCC, Level 300, Foyer           |

| 7:00 AM - 5:00 PM   | Registration – BCC                                   |

| 8:00 AM - 9:40 AM   | RMO1A RMO1B RMO1C RMO1D                              |

| 10:00 AM - 11:40 AM | RMO2A RMO2B RMO2C RMO2D                              |

| Noon – 1:20 PM      | RFIC Panel and Lunch - BCC, 307-308                  |

| 1:00 PM – 2:00 PM   | RFIC TPC Lunch Meeting – Hilton Baltimore, Holiday 4 |

| 2:20 PM - 3:40 PM   | RMO3A RMO3B RMO3C RMO3D                              |

| 4:00 PM - 5:20 PM   | RMO4A RMO4B RMO4C RMO4D                              |

#### Tuesday, 7 June 2011

| Speakers Breakfast – BCC, Level 400, Ballroom I-IV              |

|-----------------------------------------------------------------|

| Attendee Breakfast – BCC, Level 300, Foyer                      |

| Registration – BCC                                              |

| RTU1A RTU1B RTU1C                                               |

| RTU2A RTU2B RTU2C                                               |

| RFIC Panel and Lunch - BCC, 307-308                             |

| Interactive Forum – BCC, Hall A                                 |

| RFIC Steering Committee Lunch Meeting – Hilton Baltimore, Key 9 |

|                                                                 |

# **Plenary Schedule**

# Sunday, 5 June 2011 5:40 PM Baltimore Convention Center – Level 400, Ballroom III-IV Session RSU5A: RFIC Plenary Chair: David Ngo – RFMD, Inc. Co-Chairs: Albert Jerng – Ralink Technology Jacques C. Rudell - Univ. of Washington

| 5:40 PM | Welcome Message from General and TPC Chairs, RFIC Distinguished Service |

|---------|-------------------------------------------------------------------------|

|         | and Student Paper Awards                                                |

| 6:00 PM | RSU5A-1: "RF Coexistence – Challenges and Opportunities",               |

|         | Samuel Sheng, Telegent Systems                                          |

| 6:30 PM | RSU5A-2: "3G to 4G Transition – Challenges and Opportunities",          |

|         | Ron Ruebusch, Avago Technologies                                        |

#### 7:00 PM

#### Baltimore Convention Center – Level 400, Ballroom I-II Session RSU5B: RFIC Reception

# **Plenary Speaker 1:**

Samuel Sheng Chief Technical Officer and Co-Founder Telegent Systems

# **RF** Coexistence – Challenges and Opportunities

**Abstract:** The explosion in wireless technologies over the past ten years has been nothing short of staggering. WiFi, Bluetooth, ZigBee, ultrawideband, GPS, wireless HDMI, 60 GHz, and 2/3/4G cellular, along with mainstays such as FM radio and broadcast television, have become ubiquitous in consumer devices. The presence of multiple RF transceivers within a single device is now the norm, not the exception. Over the next ten years, the key challenge will shift from simply enabling wireless connectivity to enabling multiple wireless technologies to coexist at the same time in the same device, along with surviving the electromagnetic interference issues caused by the increasing complexity of such devices. While today's devices already feature several transceivers operating simultaneously, over the next ten years the problem will grow exponentially. It is projected that up to 10 RF transceivers may be active at any one time in a cellular handset, covering a frequency range anywhere from 100 MHz up to 3 GHz. This swath of spectrum is also broad enough that these radios will need to reject interference from a plethora of sources, such as microprocessors, switching regulators, LCD backlights, and touch panels. Likewise, the continuing march toward further integration will result in RF coexistence issues not only within devices, but within a single piece of silicon.

To effectively deal with this issue, many techniques will need to be developed and deployed to attack the problem in a disciplined fashion. Active interference mitigation, currently an area of research, will become a mainstay in devices and silicon. Time synchronization between radios of different standards, will become standard practice. Local oscillator and frequency planning between multiple radios will become a necessary design methodology. While currently uncommon, such techniques represent a major aspect in the development of RF technologies over the next decade.

#### About Samuel Sheng

Dr. Sheng received his BS, MS, and PhD degrees in electrical engineering, and the BA degree in applied mathematics, all from the University of California, Berkeley. Over the past 15 years, he has been involved with architecting and designing leading-edge CMOS RF and DSP chips for silicon tuners, ADSL transceivers, and DVD RF/servo technologies. In 2004, he co-founded Telegent Systems with the vision to develop complex next-generation RF SOC's such as single-chip televisions, and Dr. Sheng currently serves as Telegent's Chief Technical Officer.

Prior to co-founding Telegent Systems, Dr. Sheng was at LSI Logic and responsible for architecting and implementing a series of silicon RF tuners for video-band applications, targeted for cable modems, analog/digital video over cable, and voice over IP as well as highly integrated DVD front-end technologies. Before LSI Logic, Dr. Sheng co-led the ADSL front-end (AFE) development effort at Datapath Systems, Inc. Dr. Sheng was awarded Inventor of the Year at LSI Logic in 2002 and 2003 and was named the 2002 Distinguished Engineer at LSI Logic. He has authored numerous papers and publications on various topics such as low-power CMOS RF wireless systems and low-power CMOS digital design. He has been awarded twelve patents in the areas of RF tuner and DSL modem design.

# **Plenary Speaker 2:**

Ron Ruebusch Vice President of R&D of the Wireless Semiconductor Division Avago Technologies

#### 3G to 4G Transition – Challenges and Opportunities

**Abstract:** The cell phone industry is starting the transition from 3G to 4G networks. In this process, the number of bands that 4G radios have to accommodate is growing rapidly. As the suppliers of radio devices to the cell phone industry, the RFIC world is being challenged to provide a proliferation of new designs in a timely fashion. Without unlimited budgets, managers are being compelled to become more efficient in their product development. At the same time, as the spectrum gets more crowded emerging co-existence issues are becoming apparent which further complicate the RF front end. Lastly, our customers want increased functionality in ever smaller form factors which also raises thermal challenges. How are the successful players in this business going to successfully navigate this transition, what capabilities are required, and where are the opportunities for faster than market growth?

#### About Ron Ruebusch

Mr Ruebusch is the Vice President of R&D of the Wireless Semiconductor Division of Avago Technologies where he has been working for the last seven years. In that capacity he manages all of the RFIC product development in Avago with a team of several hundred engineers in four major locations around the world. He has over 35 years experience in the communications industry, 30 of which are in semiconductors and the last 20 of which have been in the RF segment. His background includes a broad range of executive responsibilities from division general management, marketing, sales, and R&D.

#### Monday, 6 June 2011 8:00 AM Room 337-338 Session RMO1A: Wireless Data Transceiver Architectures and Techniques Chair: Julian Tham, Broadcom Co-Chair: Li Lin, Marvell

# RM01A-1 8:00 AM

**A 2.4GHz 2Mb/s Digital PLL-based Transmitter for 802.15.4 in 130nm CMOS** M. Ghahramani<sup>1</sup>, M. P. Flynn<sup>1</sup>, M. A. Ferriss<sup>2</sup>, <sup>1</sup>University of Michigan, Ann Arbor, United States, <sup>2</sup>IBM T. J. Watson Research Center, Yorktown Heights, United States

**Abstract:** A fully integrated 2.4GHz transmitter for 802.15.4 based on a digital  $\Sigma\Delta$  fractional-N PLL is presented. A self-calibrated two-point modulation scheme enables modulation rates much larger than the loop bandwidth. An oversampled 1-bit quantizer is used as a phase detector, avoiding spurs and nonlinearity associated with some TDC-based digital PLLs. The prototype achieves an MSK modulation rate of 2Mb/s, delivers -2dBm of output power, and is free of in-band fractional spurs.

#### **RMO1A-2** 8:20 AM Full-Duplex Crystal-less CMOS Transceiver with an On-chip Antenna for Wireless Communication in Engine Controller Board of Hybrid Electric Vehicles

K. Oh<sup>1</sup>, S. Sankaran<sup>1</sup>, H. Wu<sup>1</sup>, J. Lin<sup>1</sup>, M. Hwang<sup>1</sup>, K. O<sup>2</sup>, <sup>1</sup>Silicon Microwave Integrated Circuits Research Group (SIMICS), Gainesville, United States, <sup>2</sup>Texas Analog Center of Excellence, Richardson, United States

**Abstract:** A full-duplex transceiver for wireless inter-chip data communication in an engine controller board of hybrid electric vehicles that for the first time integrates an on-chip antenna and a duplexer, as well as allowing operation without a crystal frequency reference is demonstrated. The BER degradation of RX due to the TX operation is negligible when the input power is greater than -44dBm necessary to achieve BER of less than 10-12. The transceiver fabricated in 0.13µm CMOS consumes 245mW.

#### **RMO1A-3** 8:40 AM A Fully Integrated 802.11n Radio with 24GHz Harmonic LO Generation for Low-cost, Low Power, Multi-standard Systems

R. Sadhwani<sup>1</sup>, O. Degani<sup>2</sup>, A. Ben-Bassat<sup>2</sup>, R. Banin<sup>2</sup>, H. Shang<sup>1</sup>, B. Jann<sup>1</sup>, <sup>1</sup>Intel Corporation, Hillsboro, United States, <sup>2</sup>Intel Corporation, Haifa, Israel

**Abstract:** We report a novel harmonic LOG based direct conversion RF transceiver for 802.11n radio. This multi-comm transceiver consists of Bluetooth SoC and WiFi, it includes 19-24GHz VCO, integrated front-end including WiFi T/R and WiFi-BT switches. Fabricated in 90nm digital CMOS technology, this IC consumes 422/560mW (Rx/Tx 802.11n 300/150Mbps), 110mW in BT mode, with an area of approx 19mm<sup>2</sup>. A peak saturated power of 24/9dBm is achieved at antenna in WiFi/BT mode.

#### **RMO1A-4** 9:00 AM Digital RF Receiver Front-end with Wideband Operation Capability for m-WiMAX

H. Seo<sup>1</sup>, I. Choi<sup>1</sup>, C. Park<sup>2</sup>, J. Yoon<sup>2</sup>, B. Kim<sup>1</sup>, <sup>1</sup>Pohang University of Science and Technology, Pohang, Republic of Korea, <sup>2</sup>Samsung Electronics, Suwon, Republic of Korea

**Abstract:** A Digital RF receiver front-end with wideband operation capability is presented for m-WiMAX application. By employing sampling mixer and discrete-time filter, the receiver operates in charge domain. In addition to flexibility of the discrete-time (DT) filter, the new Non-Decimation Finite Impulse Response (FIR) filter can be cascaded to a conventional FIR filter. And we can easily increase the order of the sincn-type filtering response to achieve wideband signal process capability.

# **RMO1A-5** 9:20 AM A QPLL-Timed Direct-RF Sampling Band-Pass $\Sigma\Delta$ ADC with 1.2GHz Tuning Range in 0.13µm CMOS

S. Gupta<sup>1</sup>, D. Gangopadhyay<sup>1</sup>, H. Lakdawala<sup>2</sup>, J. C. Rudell<sup>1</sup>, D. J. Allstot<sup>1</sup>, <sup>1</sup>University of Washington, Seattle, United States, <sup>2</sup>Intel Corporation, Hillsboro, United States

**Abstract:** A direct-RF sampled band-pass  $\Sigma\Delta$  modulator implemented in 0.13µm CMOS enables reconfigurable RF A/D conversion. It features a programmable narrow-band Q-enhanced low-noise amplifier and a phase-locked loop with quadrature outputs synchronized with the ADC. It consumes 41mW and achieves an SNDR of 40-50dB and IIP3 of -5/-7dBm over the 0.8-2GHz frequency band. Measured PLL phase noise is -113dBc/Hz at a 1MHz offset frequency with a -74.5dBc spur; RMS period jitter is 1.38ps.

#### Monday, 6 June 2011 8:00 AM Room 339-340 Session RMO1B: Digital to RF and Sigma-Delta Transmit Modulators Chair: Noriharu Suematsu, Tohoku University Co-Chair: Gernot Hueber, NXP Semiconductors

#### **RMO1B-1** 8:00 AM All-Digital Transmitter based on ADPLL and Phase Synchronized Delta Sigma Modulator

J. Chen, L. Rong, F. Jonsson, L. Zheng, Royal Institute of Technology (KTH), Stockholm, Sweden

**Abstract:** A novel architecture of all-digital polar transmitters is proposed, mainly composed of an ADPLL for phase modulation, a low-pass Sigma Delta modulator for envelope modulation and a class-D PA. The low noise ADPLL and high oversampling rate relief filter design, enabling the use of a on-chip filter. The differential coding scheme enhances the fundamental tone and suppresses the DC and high harmonics. It was fabricated in a 90nm CMOS process, occupying 1.4 mm<sup>2</sup>. Measurements justify the concept.

#### **RMO1B-2** 8:20 AM A 0.7-3GHz Envelope Delta-sigma Modulator Using Phase Modulated Carrier Clock for Multi-mode/band Switching Amplifiers

S. Hori, K. Kunihiro, K. Takahashi, M. Fukaishi, NEC Corporation, Kawasaki, Japan

**Abstract:** A 1-bit RF modulator using phase-modulated-carrier-clocking envelope delta-sigma modulation for a multi-mode/band transmitter is presented. The prototype IC designed in 90nm CMOS process covers 2.4GHz ISM and 3GPP frequency bands up to 3GHz in conformity with IEEE 802.11g, W-CDMA and LTE in 5MHz-mode. The IC dissipates 8mW for 1.95GHz WCDMA and occupies 0.044mm<sup>2</sup>.

#### RM01B-3 8:40 AM

# A 12-bit Resolution, 200-MSample/second Phase Modulator for a 2.5GHz Carrier with Discrete Carrier Pre-Rotation in 65nm CMOS

T. W. Barton, S. Chung, P. A. Godoy, J. L. Dawson, Massachusetts Institute of Technology, Cambridge, United States

**Abstract:** A digital-to-RF phase modulator based on a single current-steering DAC is presented, including a carrier pre-rotation scheme that prevents phase inaccuracy due to carrier feedthrough. The phase modulator has been fabricated in a standard 65nm CMOS process and draws 1.9mW from a 1V supply. The modulator achieves 12bit resolution at a measured 200MSamples/second, state-of-the-art performance in both resolution and sampling speed.

#### **RMO1B-4** 9:00 AM A Direct Sampling Mixer with Complex Coefficient Transfer Function in 65nm CMOS

Y. Morishita<sup>1</sup>, T. Morita<sup>1</sup>, N. Saito<sup>1</sup>, K. Araki<sup>2</sup>, <sup>1</sup>Panasonic Corporation, Yokohama, Japan, <sup>2</sup>Tokyo Institute of Technology, Tokyo, Japan

**Abstract:** The Direct Sampling Mixer (DSM) with complex coefficient transfer function is demonstrated. The operation theory and the detail design methodology are discussed for the 2-pararell architecture, which can achieve large image rejection by introducing the attenuation pole at the image frequency. The proposed architecture was fabricated in a 65nm CMOS process. The measured results agree well with the theory, which proves the validity of the proposed architecture and the design methodology.

#### RMO1B-5 9:20 AM Multiband Mixed-Signal Vector Modulator IC

U. Mayer, M. Wickert, R. Eickhoff, F. Ellinger, Technische Universitaet Dresden, Dresden, Germany

**Abstract:** This paper presents an active BiCMOS vector modulator suitable for WLAN diversity transceivers. It features a LNA, a SPI and 8-bit DACs for vector control and internal references and thus is suitable as a monolithic IC for RF signal weighting. When mounted on a PCB, it delivers a maximum gain of 12dB at 5.6GHz. It draws a current of 17mA from a 3.3V supply. The whole design is free of bulky inductors thus requiring an area of only 1.3 mm<sup>2</sup>.

#### Monday, 6 June 2011 8:00 AM Room 341-342 Session RMO1C: mm-Wave Communication Systems Chair: Luciano Boglione , SSSC/AFRL Co-Chair: Georg Boeck, Berlin Institute of Technology

#### RMO1C-1 8:00 AM Indoor and Outdoor mm-Wave Systems and RF/BB SoCs (Invited Paper)

A. Matsuzawa, K. Okada, Tokyo Institute of Technology, Meguro-ku, Japan

**Abstract:** This paper gives an overview of the mm-Wave Project to realize the indoor and the outdoor systems over Gbps by developing CMOS RF and Baseband SoCs. A 60GHz direct conversion transceiver was developed using 65nm CMOS and demonstrates 7Gbps using 16QAM. A quadrature VCO attained very low phase noise of -94dBc/Hz @1MHz. For the outdoor system (1km), a baseband mixed signal SoC using 90nm CMOS was developed and demonstrates 600Mbps with 16QAM in 38GHz (BW: 260MHz) band.

#### **RMO1C-2 8:20 AM** A 60-GHz RF IQ DAC Transceiver with on-Die at-Speed Loopback

E. Laskin, A. Tomkins, A. Balteanu, I. Sarkas, S. P. Voinigescu, University of Toronto, Toronto, Canada

**Abstract:** A transceiver with direct 5.3Gb/s carrier modulation using a 60GHz 2-bit IQ DAC, a zero-IF IQ receiver, a PLL with a single 60GHz VCO and an integrated crystal oscillator, was designed and fabricated in a 130nm SiGe BiCMOS technology. It covers the entire 57-66 GHz band with digitallyprogrammable 0 to 10 dBm output power and -15 to 60 dB receiver gain, and 5-6dB noise figure. Depending on the receive-path gain, the IP1 varies between -55 and 0dBm. The chip consumes 350/225mW in TX/RX mode.

#### **RMO1C-3 8:40 AM** A 60GHz Digitally Controlled RF Beamforming Array in 65nm CMOS with Off-Chip Antennas

S. Lin<sup>1</sup>, K. Ng<sup>2</sup>, H. Wong<sup>2</sup>, K. Luk<sup>2</sup>, S. Wong<sup>1</sup>, A. Poon<sup>1</sup>, <sup>1</sup>Stanford University, Stanford, United States, <sup>2</sup>City University of Hong Kong, Hong Kong, China

**Abstract:** An RF path 60GHz band 4element array using proposed phase-oversampling vector modulation is implemented in 65nm CMOS. Digital controlled semi-lookup table method is proposed to compensate for non-idealities in circuits, antenna array, and interfaces. Accurate and high resolution control on the gain and phase is demonstrated. The receiver features an NF of 5.6 dB and 3.5° phase resolution at a backoff of 3dB. It dissipates 178mW from 1V supply and obtains 18.5dB gain for each channel.

#### **RMO1C-4** 9:00 AM A 60dB Gain and 4dB Noise Figure CMOS V-Band Receiver Based on Two-Dimensional Passive Gm-Enhancement

N. Wang<sup>1</sup>, H. Wu<sup>1</sup>, J. Y. Liu<sup>1</sup>, J. Lu<sup>1</sup>, H. Hsieh<sup>2</sup>, P. Wu<sup>2</sup>, C. Jou<sup>2</sup>, M. F. Chang<sup>1</sup>, <sup>1</sup>University of California Los Angeles, Los Angeles, United States, <sup>2</sup>Taiwan Semiconductor Manufacturing Company, Hsinchu, Taiwan

**Abstract:** A direct conversion receiver which consists of LNA, mixer and programmable gain amplifier (PGA) for V-band (60GHz) applications is designed and realized in 65nm CMOS. A novel two-dimensional passive gm-enhancement technique is devised to boost the conversion gain and lower the Noise Figure (NF) with insignificant power overhead. An overall minimum SSB NF of 3.9dB and a maximum power conversion gain of 60dB is achieved with an area of 0.2mm<sup>2</sup> and 34mW of power dissipation.

#### **RMO1C-5 9:20 AM** A 220GHz Subharmonic Receiver Front End in a SiGe HBT Technology

E. Ojefors<sup>1</sup>, B. Heinemann<sup>2</sup>, U. R. Pfeiffer<sup>1</sup>, <sup>1</sup>University of Wuppertal, Wuppertal, Germany, <sup>2</sup>IHP GmbH, Frankfurt (Oder), Germany

**Abstract:** A monolithic 220GHz receiver front end manufactured in an engineering version of a fT/fmax = 280/435-GHz SiGe technology is presented. The front end consists of a three-stage differential LNA and a subharmonic mixer. A breakout of the 220GHz LNA provides 15dB gain and a bandwidth of 28GHz. The integrated downconverter yields a conversion gain of 15dB, a 15dB DSB NF, and a 30GHz bandwidth when pumped with a 0dBm, 110GHz LO signal.

#### Monday, 6 June 2011 8:00 AM Room 343-344 Session RMO1D: Frequency Synthesis: 60GHz and Beyond Chair: Stefano Pellerano, Intel Corp. Co-Chair: Jaber Khoja, Zoran

#### **RMO1D-1** 8:00 AM A 60GHz Wideband Injection-Locked Frequency Divider with Adaptive-Phase-Enhancing Technique

H. Wang<sup>1</sup>, L. Zhang<sup>1</sup>, D. Yang<sup>1</sup>, D. Zeng<sup>2</sup>, L. Zhang<sup>1</sup>, Y. Wang<sup>1</sup>, Z. Yu<sup>1</sup>, <sup>1</sup>Tsinghua University, Beijing, China, <sup>2</sup>Chinese Academy of Sciences, Suzhou, China

**Abstract:** A 60GHz injection-locked frequency divider (ILFD) with quadrature outputs is designed in 90nm CMOS technology. An adaptive coupling scheme is proposed to enlarge the phase shift for a wideband locking range. The measured results exhibit an input locking range of 12.1GHz or 20.5% from 52.7 to 64.8GHz at an incident power of 0dBm. The core circuit consumes 8.6mW from a 1.2V power supply and occupies an area of 360x230µm.

## **RM01D-2** 8:20 AM A 100GHz Phase-Locked Loop in 0.13µm SiGe BiCMOS process

S. Kang, J. Chien, A. M. Niknejad, University of California at Berkeley, Berkeley, United States

**Abstract:** A fully integrated 100GHz PLL is demonstrated in 0.13µm SiGe BiCMOS process. The PLL employs a fundamental-frequency differential Colpitts voltage-controlled oscillator with 8.3% tuning range, which achieves a phase noise of -124.5dBc/Hz at 10MHz offset, and a single-ended output power of 3dBm. The total lock range of the PLL is from 92.7 to 100.2GHz, the phase noise is - 102dBc/Hz at 1MHz offset, and reference spurs are not observable. The PLL dissipates 570mW and occupies 1.21mm<sup>2</sup>.

#### **RMO1D-3** 8:40 AM W-Band Frequency Synthesis Using a Ka-Band PLL and Two Different Frequency Triplers

Z. Chen, C. Wang, P. Heydari, University of California, Irvine, Irvine, United States

**Abstract:** Two chips for 96GHz frequency generation employ the same Ka-band PLL and (1) an injection-locked frequency tripler; (2) a harmonic-based frequency tripler in 0.18µm SiGe BiCMOS are presented. The ILFT and HBFT preceded by the same Ka-band PLL achieve measured phase noise of -93dBc/Hz and -92dBc/Hz at 1MHz offset, respectively. Both chips have the same power consumption of 140mW from 1.8V/2.5V supplies.

#### **RMO1D-4** 9:00 AM 60GHz CMOS Divide by 5 Injection-Locked Frequency Divider with an Open-Stub-Loaded Floating-Source Injector

M. Li, H. Kuo, T. Huang, H. Chuang, National Cheng Kung University, Tainan, Taiwan

**Abstract:** A new injector topology is adopted for the design of a 60GHz divide-by-5 injection-locked frequency divider (ILFD). The topology is based on a distributed-element harmonic termination by an open-stub structure connected to the floating source end of the injection pair. With this topology together with an NMOS cross-coupled oscillator core, the supply voltage and power consumption of the ILFD can be greatly reduced, and the locking range of the designed ILFD has been greatly extended by over 70%.

#### Monday, 6 June 2011 10:00 AM Room 337-338 Session RMO2A: WiMedia UWB and IR-UWB Receivers and Transmitters Chair: Domine Leenaerts, NXP Semiconductors Co-Chair: Yann Deval , IMS Lab

#### **RMO2A-1** 10:00 AM A 65nm CMOS Low-Noise Three Band Group WiMedia UWB Receiver

W. Ko, H. Shin, S. Ko, J. Yim, B. Kang, T. Kim, I. Ryu, S. Yang, J. Bae, H. Park, Samsung Electronics Co., Ltd, Yongin, Republic of Korea

**Abstract:** A low-noise and high-gain ultra wideband (UWB) receiver was developed using a 65nm CMOS technology. In order to enhance the gain and noise figure, the resistive feedback amplifier and two cascode stages with the inductive load resonating at three different frequencies are employed. The fabricated UWB receiver showed an average high gain of 72.6dB and a noise figure of 4.1-5.8dB in three band groups. The measured sensitivities in three band groups meet all WiMedia PHY specifications.

#### **RMO2A-2 10:20 AM** A WiMedia UWB Transmitter up to 9GHz in 65nm CMOS and Wafer-level Fabricated Package

J. Yim, B. Kang, T. Kim, W. Ko, H. Shin, S. Ko, I. Ryu, S. Yang, J. Bae, H. Park, Samsung Electronics, Yongin, Republic of Korea

**Abstract:** A 3.1-4.7GHz and 6.3-9GHz RF transmitter fabricated in a 65nm CMOS technology and packaged with a Wafer-level Fabricated Package (WFP) is presented. For high frequency and wideband performances, all the effects of package are considered and loopback paths with a power detector are implemented. A new structure of T/R switch is devised for the low noise performance of Rx and the high linearity of Tx. With these circuits, the transmitter features high linearity, low power consumption.

#### **RMO2A-3** 10:40 AM Low Power, Fully Differential SiGe IR-UWB Transmitter and Correlation Receiver ICs

D. Lin, A. Trasser, H. Schumacher, Ulm University, Ulm, Germany

**Abstract:** In this paper a 3.1-10.6 GHz impulse-radio ultra-wideband (IR-UWB) transmitter and a correlation receiver are presented. The transmitter comprises a differential impulse generator mounted chip-on-board on a dipole fed circular slot antenna. The receiver front-end, mounted at the feed-point of another dipole antenna, is realized with a differential low noise amplifier, an analog correlator and a template impulse generator. Measurement results show a motion tracking capability in the mm range.

#### **RMO2A-4** 11:00 AM A 520pJ/pulse IR-UWB Radar for Short Range Object Detection

Y. Shim, S. Yuwono, S. Kim, J. Kim, S. Han, S. Lee, KAIST, Daejeon, Republic of Korea

**Abstract:** This paper presents a low power, low complexity IR-UWB radar transceiver for short range object detection. The transceiver provides robustness against false detections without increasing power consumption, chip size, or complexity. The receiver and the transmitter dissipate only 50 and 470pJ/pulse, respectively. The measured TX pulse spectrum shows -58dBm maximum power and 1GHz bandwidth with 4GHz center frequency. The sensitivity is -45dBm, and the measured RX is fully functional for detecting.

#### RMO2A-5 11:20 AM A Self-Synchronized, Crystal-less, 86µW, Dual-Band Impulse Radio for Ad-Hoc Wireless Networks

X. Y. Wang, R. K. Dokania, Y. Zhuang, C. I. Dorta-Quinones , W. Godycki, M. Lyons, A. B. Apsel, Cornell University, Ithaca, United States

**Abstract:** An 86µW, 150Kbps, self synchronizing 3.5-4.5GHz UWB IR transceiver is presented. Synchronous receiver duty cycling of 0.5% is enabled without a crystal through a pulse coupled oscillator (PCO) network that establishes timing and allows multi-node multi-hop communication. The synchronization scheme is supported by implementation of a low power oscillator and timing circuits to control duty-cycling. Our FCC compliant transceiver uses OOK modulation and has a receiver sensitivity of -86dBm.

#### Monday, 6 June 2011 10:00 AM Room 339-340 Session RMO2B: Cellular RF Chair: Didier Belot, ST-Microelectronics Co-Chair: Marc Tiebout, Infineon Technologies

#### RM02B-1 10:00 AM Single-Chip Multi-band SAW-less LTE WCDMA and EGPRS CMOS Receiver with Diversity

H. Xie, P. Rakers, R. Fernandez, T. Mccain, J. Xiang, J. Parkes, J. Riches, R. Verellen, M. Rahman, E. Shimoni, V. Bhan, D. B. Schwartz, Fujitsu Semiconductor Wireless Products Inc., Tempe, United States

**Abstract:** A single-chip multi-mode multi-band saw-less 90nm CMOS receiver is designed and implemented for 4G mobile platform. It supports LTE/WCDMA/EGPRS standards. The receiver achieves a typical 3dB and maximum 4dB noise figure (NF) in all standards and bands. It also automatically calibrates baseband low-pass filter cut-off frequency, mixer image rejection and IIP2 performance.

#### **RMO2B-2** 10:20 AM An L-Band Receiver-Frontend-Architecture using Adaptive Q-Enhancement Techniques in 65nm CMOS as Enabler for Single-SAW GPS Receivers C. Schultz<sup>1</sup>, H. Doppke<sup>1</sup>, M. Hammes<sup>1</sup>, R. Kreienkamp<sup>1</sup>, L. Lemke<sup>1</sup>, S. van Waasen<sup>2</sup>, <sup>1</sup>Infineon Technologies AG, Duisburg, Germany, <sup>2</sup>Forschungszentrum Jülich, Jülich, Germany

**Abstract:** A GPS receiver front-end achieves high dynamic input range by using Q-enhancement circuitry. In mobile phone environments the Q of the LNA is automatically increased, improving blocker performance by 11.3dB. The area is 1.9mm<sup>2</sup> in 65nm CMOS without RF options and requires 25mA from a 1.3V supply with a system NF of 1.5dB.

#### RMO2B-3 10:40 AM Reconfigurable Wide-band Receiver with Positive Feed-back Translational Loop

C. Izquierdo<sup>1</sup>, A. Kaiser<sup>2</sup>, F. Montaudon<sup>1</sup>, P. Cathelin<sup>1</sup>, <sup>1</sup>ST Ericsson, Crolles, France, <sup>2</sup>IEMN, Lille, France

**Abstract:** A wide-band receiver for multi-standard cellular applications with a positive feed-back translational loop is presented in this paper. This technique allows tunable RF filtering right on input node of the LNA. The 65nm CMOS prototype circuit achieves, when in WCDMA mode, attenuation of out-of-band interferers of 12dB at 20MHz frequency offset, improving the out-of-band IIP3 by 17dB. The packaged test-chip provides good performance over a very wide frequency range from 1.3GHz to 2.85GHz.

#### **RMO2B-4** 11:00 AM A Digital Calibration Enhanced GSM/GPRS Transmitter

P. Wang, C. Wang, W. Lee, T. Yu, Mediatek, Hsin-Chu, Taiwan

**Abstract:** This paper presents a digital calibration enhanced transmitter that is capable of selfcalibrating loop gain and the non-linearity of the VCO gain of a charge pump PLL in a pre-emphasis transmitter. The results shows that we can achieve 0.5 degree phase error and -68dBc ORFS for GMSK modulation, which prove that the accuracy of the loop gain calibration and VCO gain linearity is within 1%, and two times reduction compared to all digital and analog transmitters.

#### **RMO2B-5** 11:20 AM High Efficiency Envelope Tracking Power Amplifier with Very Low Quiescent Power for 20MHz LTE

M. Hassan<sup>1</sup>, M. Kwak<sup>1</sup>, V. W. Leung<sup>2</sup>, C. Hsia<sup>1</sup>, J. J. Yan<sup>1</sup>, D. F. Kimball<sup>1</sup>, L. E. Larson<sup>1</sup>, P. M. Asbeck<sup>1</sup>, <sup>1</sup>University of California at San Diego, La Jolla, United States, <sup>2</sup>Qualcomm Inc., San Diego, United States

**Abstract:** A high efficiency wideband envelope tracking (ET) power amplifier (PA) with low quiescent power is presented. The CMOS envelope amplifier (EA) has a combined linear amplifier (IA) and switching amplifier to achieve high efficiency and wider bandwidth. Quiescent power of the EA is reduced using a source cross-coupled LA with inherently low DC power dissipation. Measurements show a power added efficiency of 45% for the ET PA for 20MHz LTE signal with 6dB PAPR at 2.5GHz at 1W output power.

#### Monday, 6 June 2011 10:00 AM Room 341-342 Session RMO2C: Advanced Architecture PAs Chair: Eddie Spears, RFMD Co-Chair: Jeffrey Walling, Rutgers University

#### **RMO2C-1 10:00 AM** A W-band Current Combined Power Amplifier with 14.8dBm Psat and 9.4% Maximum PAE in 65nm CMOS

Z. Xu<sup>1</sup>, Q. J. Gu<sup>2</sup>, M. F. Chang<sup>3</sup>, <sup>1</sup>HRL Laboratories, Malibu, United States, <sup>2</sup>University of Florida, Gainesville, United States, <sup>3</sup>University of California, Los Angeles, Los Angeles, United States

**Abstract:** We present a fully differential 101-117GHz power amplifier(PA) using two way current power combiner in 65nm bulk CMOS. It delivers up to 14.8dBm saturated output power with over 14dB power gain and better than 9.4% power added efficiency (PAE), which also achieves better than 11.6dBm output P1dB. A current power combiner is employed to combine the power from two separate PAs. The entire PA core occupies 0.106 mm2 chip area and dissipates 200mW.

#### RMO2C-2 10:20 AM X-to-K band Broadband Watt-level Power Amplifier Using Stacked-FET Unit Cells

Y. Park, Y. Kim, W. Choi, J. Woo, Y. Kwon, Seoul National University, Seoul, Republic of Korea

**Abstract:** A broadband watt-level stacked-FET power amplifier (PA) has been developed using 0.15µm GaAs pHEMT's. A triple-stacked FET structure is used as a unit cell to combine RF voltage swings to achieve high-output power and broad bandwidth at the same time. The fabricated PA shows a peak power of 33.7dBm with a power added efficiency (PAE) of 29.5% at frequency of 18GHz, and higher than 32dBm output power from 10 to 21GHz. The fractional 3dB output power bandwidth is 84%.

#### **RMO2C-3** 10:40 AM Wideband High Efficiency Envelope Tracking Integrated Circuit for Micro-Base Station Power Amplifiers

M. Kwak<sup>1</sup>, D. F. Kimball<sup>1</sup>, C. D. Presti<sup>2</sup>, A. Scuderi<sup>3</sup>, C. A. Santagati<sup>3</sup>, J. J. Yan<sup>1</sup>, P. M. Asbeck<sup>1</sup>, L. E. Larson<sup>1</sup>, <sup>1</sup>University of California at San Diego, La Jolla, United States, <sup>2</sup>Qualcomm Inc., San Diego, United States, <sup>3</sup>STMicroelectronics

**Abstract:** This paper presents a high performance BCD (Bipolar-CMOS-DMOS) monolithic envelope tracking (ET) IC to achieve high efficiency and linearity for micro-base station power amplifier (PA) applications. Measurement of the BCD high voltage envelope amplifier shows an efficiency of 72% using WCDMA input signals (7.7dB PAR). An ET PA has overall drain efficiency above 51%, with an ACLR1 of -49dBc using memory mitigation digital pre-distortion, at an average output power above 2W and a gain of 10dB.

#### **RMO2C-4** 11:00 AM A Power-Combined Switched-Capacitor Power Amplifier in 90nm CMOS

S. Yoo<sup>1</sup>, J. S. Walling<sup>2</sup>, E. Woo<sup>1</sup>, D. J. Allstot<sup>1</sup>, <sup>1</sup>University of Washington, Seattle, United States, <sup>2</sup>Rutgers University, New Brunswick, United States

**Abstract:** A digitally-controlled switched-capacitor RF power amplifier (SCPA) is implemented with a transformer-based power-combiner in 90nm CMOS. The individual SCPA cores can be controlled to provide high average output power and linearity in an all-switching mode or increased dynamic range in a sequential-switching mode. It delivers a peak (average) output power of 27.0 (20.3) dBm with a peak (average) PAE of 31.3% (18.2%) for a 64QAM OFDM modulated signal with measured EVM=3.8% in the 2.4GHz band.

#### **RMO2C-5** 11:20 AM A 1.8GHz Wide-Band Stacked-Cascode CMOS Power Amplifier for WCDMA Applications in 65nm Standard CMOS

S. Leuschner<sup>1</sup>, J. Mueller<sup>2</sup>, H. Klar<sup>1</sup>, <sup>1</sup>Technical University of Berlin, Berlin, Germany, <sup>2</sup>Infineon Technologies AG, Neubiberg, Germany

**Abstract:** A two-stage power amplifier (PA) for WCDMA operation in standard 65nm CMOS is presented. The power amplifier delivers a saturated output power of 29.4dBm at a PAE of 51% at 1.8GHz. A two-stage interstage matching network was employed to achieve a high bandwidth (300MHz) where the amplifier shows a PAE 45%. With a WCDMA signal a maximum linear output power of 25.4dBm (PAE=37.9%) was measured without digital predistortion (DPD). Using DPD, these figures could be improved to 27.9dBm and 48%.

#### Monday, 6 June 2011 10:00 AM Room 343-344 Session RMO2D: Emerging RFIC Device Technologies Chair: Aditya Gupta, Northrop Grumman Co-Chair: Eli Reese, Triquint

#### **RMO2D-1 10:00 AM** Non-invasive Monitoring of CMOS Power Amplifiers Operating at RF and mm-Wave Frequencies using an On-chip Thermal Sensor

J. Gonzalez<sup>1</sup>, B. Martineau<sup>2</sup>, D. Mateo<sup>T</sup>, J. Altet<sup>1</sup>, <sup>1</sup>Universitat Politècnica de Catalunya, Barcelona, Spain, <sup>2</sup>ST Microelectronics, Grenoble, France

**Abstract:** In this paper a non-invasive technique for the on-chip observation of PA operation is presented. It uses a differential temperature sensor that transduces the temperature increase due to the power dissipated by active transistors operating at high frequencies into a low frequency signal that is proportional to some relevant PA figures of merit, such as output power or PAE. The technique is demonstrated by using the same thermal sensor in two 65nm CMOS different PAs (a 2GHz PA and a 60GHz PA)

#### **RMO2D-2** 10:20 AM High-Power Digital Controlled Artificial Dielectric GaN Reconfigurable Transmission Lines for Digitally Assisted RFICs

M. K. Watanabe, T. R. LaRocca, Northrop Grumman Aerospace Systems, Redondo Beach, United States

**Abstract:** The first known GaN implementation of high-power digital controlled artificial dielectric (DiCAD) reconfigurable transmission lines is presented. Standard GaN HEMT processing techniques were used, making DiCAD easily compatible with future circuit designs. The DiCAD transmission line's effective dielectric constant exhibits linear digital control from 15 to 32 with 3-bit resolution up to 50GHz. P1dB is measured to be 27dBm and OIP3 is calculated to be 48dBm for all states.

# RM02D-3 10:40 AM

#### A New Method to Achieve RF Linearity in SOI Nanowire MOSFETs

A. Razavieh<sup>1</sup>, N. Singh<sup>2</sup>, A. Paul<sup>1</sup>, G. Klimeck<sup>1</sup>, D. B. Janes<sup>1</sup>, J. Appenzeller<sup>1</sup>, <sup>1</sup>Purdue University, West Lafayette, United States, <sup>2</sup>Agency For Science, Technology And Research (A\*STAR), Singapore

**Abstract:** In this paper we show that device level linearity can be achieved if transistors operate in 1-D ballistic transport regime in the quantum capacitance limit. We consider SOI Silicon nanowire MOSFETS and report the IIP3 of about -13dBm for this regime of operation. When normalized the IIP3 values to the power at maximum transconductance 10dB improvement compare to operation in velocity saturation regime is achieved.

#### **RMO2D-4** 11:00 AM Nano Crossbar Electrostatic Discharge Protection for RF ICs

J. Liu<sup>1</sup>, L. Zhang<sup>2</sup>, X. Wang<sup>1</sup>, L. Lin<sup>1</sup>, Z. Shi<sup>1</sup>, A. Wang<sup>1</sup>, R. Huang<sup>2</sup>, Y. Cheng<sup>2</sup>, <sup>1</sup>University of California, Riverside, Riverside, United States, <sup>2</sup>Peking University, Beijing, China

**Abstract:** We report design and analysis of new nano crossbar based nano phase switching electrostatic discharge (ESD) protection structures. Measurements confirm ESD protection featuring fast response of 100pS, ultra low leakage Ileak~0.11pA, varying trigger voltage (Vt1) and good ESD protection voltage ratio (ESDV) 230V/µm<sup>2</sup>. This nontraditional nano-crossbar ESD protection can be a potential solution for RF and mixed-signal ICs.

#### **RMO2D-5** 11:20 AM An All-Graphene Radio Frequency Low Noise Amplifier

S. Das<sup>1</sup>, J. Appenzeller<sup>2</sup>, <sup>1</sup>Purdue University, West Lafayette, United States, <sup>2</sup>Purdue University, West Lafayette, United States

**Abstract:** In this paper, we propose and quantitatively evaluate an "All-Graphene nano-ribbon (GNR) circuit" for high frequency low noise amplifier (LNA) applications, which shows considerable advantage over state-of—the-art technologies. In particular, we discuss how to satisfy the requirements for temperature stability, gain, power dissipation, noise and speed for a high performance LNA circuit by adjusting only the width of the nano ribbons.

#### Monday, 6 June 2011 2:20 PM Room 337-338 Session RMO3A: Low Power Wireless Sensor Techniques Chair: Glenn Chang, MaxLinear Co-Chair: Ali Afsahi, Broadcom

#### **RMO3A-1** 2:20 PM A 30MHz-2.4GHz CMOS Receiver with Integrated RF Filter and Dynamicrange-scalable Energy Detector for Cognitive Radio

M. Kitsunezuka<sup>1</sup>, H. Kodama<sup>1</sup>, N. Oshima<sup>1</sup>, K. Kunihiro<sup>1</sup>, T. Maeda<sup>2</sup>, M. Fukaishi<sup>1</sup>, <sup>1</sup>NEC Corporation, Kawasaki, Japan, <sup>2</sup>Renesas Electronics Corporation, Kawasaki, Japan

**Abstract:** A 30MHz-2.4GHz CMOS receiver with a highly linear integrated tunable RF filter, as well as with a dynamic-range-scalable RSSI-based energy detector for both whitespace and interference-level sensing, is reported. The test chip, fabricated in 90nm CMOS process, achieves over 42dB harmonic rejection including seventh-order harmonic without any external device, 67dB gain, 5-8dB NF, +1.7dBm in-band IIP3, and +37dBm IIP2 while drawing only 25-37mA from 1.2V supply.

#### **RMO3A-2 2:40 PM** A 1900MHz-Band GSM-Based Clock-Harvesting Receiver with -87dBm Sensitivity

J. K. Brown, D. D. Wentzloff, University of Michigan, Ann Arbor, United States

**Abstract:** A 0.13µm CMOS clock-harvesting receiver is presented which extracts a 21Hz clock embedded within the GSM standard for the wake-up of a wireless sensor network. In active mode, the receiver achieves -87dBm sensitivity with 57µs of jitter at the output while consuming 126µW. The receiver is optimized for heavy duty-cycling with a sleep-mode power consumption of only 81pW.

#### **RMO3A-3 3:00 PM** A CMOS Spectrum Sensor Using Injection Locking of Two Voltage-Controlled Oscillators for Cognitive Radio System

F. Wang<sup>1</sup>, C. Chen<sup>1</sup>, J. Tsai<sup>1</sup>, T. Horng<sup>1</sup>, K. Peng<sup>2</sup>, J. Je-Kuan<sup>3</sup>, J. Li<sup>3</sup>, C. Chen<sup>3</sup>, <sup>1</sup>Department of Electrical Engineering, Kaohsiung, Taiwan, <sup>2</sup>Department of Computer and Communication Engineering, Kaohsiung, Taiwan, <sup>3</sup>Info. and Comm. Re Research Lab., Hsinchu, Taiwan

**Abstract:** This paper presents a CMOS spectrum sensor to detect spectral usage and spectrum holes for cognitive radio system. The sensor consists of a swept oscillator and a frequency discriminator, both of which use the injection locking of VCO to process the sensed signal without requiring a frequency synthesizer. The sensor can detect the frequency and power for wireless communication signals with high accuracy at a spectrum scanning speed of 100MHz/ms. The sensitivity can be below -100dBm.

#### **RMO3A-4 3:20 PM** A Wirelessly-Powered Passive RF CMOS Transponder with Dynamic Energy Storage and Sensitivity Enhancement

Z. Safarian, H. Hashemi, University of Southern California, Los Angeles, United States

**Abstract:** A new scheme for a passive sensor is proposed in this work in which the extra received power beyond the sensitivity level is stored and later used to enhance the sensitivity of the sensor. The chip prototype has been designed and fabricated in a 130nm CMOS technology. The measurement results show the sensitivity of the implemented sensor is improved from -19.5dBm to -29dBm at 900MHz, and from -15.4dBm to -26.5dBm at 2.4GHz.

#### Monday, 6 June 2011 2:20 PM Room 339-340 Session RMO3B: Low Power LNA Design Techniques Chair: Danilo Manstretta, University of Pavia Co-Chair: Jean-Baptiste Begueret, University of Bordeaux

# **RMO3B-1** 2:20 PM A 60μW LNA for 2.4GHz Wireless Sensors Network Applications

T. Taris, J. Begueret, Y. Deval, University of Bordeaux, Talence, France

**Abstract:** This work reports on the implementation of a 2.4GHz ultra-low power (ULP) low noise amplifier (LNA) in a standard CMOS 0.13µm process. The proposed design methodology consists of optimizing the tradeoff between RF performance and current consumption of a MOS transistor. The supply of the circuit, controlled by a 3bit DAC, varies from 0.4 to 0.6 V. Experimental results of the circuit indicate a power dissipation of 60µW@0.4V, a noise figure of 5.3dB, and a forward gain of 13.1dB.

#### RMO3B-2 2:40 PM A 1.5V, 140µA CMOS Ultra-Low Power Common-Gate LNA

C. Jeong<sup>1</sup>, W. Qu<sup>2</sup>, Y. Sun<sup>1</sup>, D. Yoon<sup>1</sup>, S. Han<sup>1</sup>, S. Lee<sup>1</sup>, <sup>1</sup>Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Republic of Korea, <sup>2</sup>Silicon Works Company Ltd, Daejeon, Republic of Korea

**Abstract:** This paper presents design guidelines for ultra-low power Low Noise Amplifier design by comparing input matching, gain, and noise figure characteristics of common-source and commongate (CG) topologies. A current-reused ultra-low power 2.2GHz CG LNA is implemented based on 0.18µm CMOS technology. Measurement results show 13.9dB power gain, 5.14dB NF, and -9.3dBm IIP3, respectively, while dissipating 140µA from a 1.5V supply, which shows best FOM among all published ultra-low power LNAs.

#### **RMO3B-3 3:00 PM** Effects of the Nonlinearity of the Common-Gate Stage on the Linearity of CMOS Cascode Low Noise Amplifier

C. Cui, T. Kim, S. Kim, B. Kim, Sungkyunkwan University, Suwon, Republic of Korea

**Abstract:** This work presents the effects of the CG stage nonlinearity on the linearity of the cascode LNA. Conventionally, the CG stage is assumed as an ideal current buffer in cascode LNA, but the analysis shows that the CG stage limits the linearity of cascode LNA as the gain increases. Therefore, the simple linearization of the CS stage has difficulties to enhance the gain of LNA as frequency increases. The analysis and measurement show that optimal load impedance that maximizes OIP3 of the LNA exists.

#### **RM03B-4 3:20 PM** A 1.3mW 20dB Gain Ultra Low Power Inductorless LNA with 4dB Noise Figure for 2.45GHz ISM Band

F. Belmas<sup>2</sup>, F. Hameau<sup>2</sup>, J. Fournier<sup>1</sup>, <sup>1</sup>IMEP, Grenoble, France, <sup>2</sup>CEA, Grenoble, France

**Abstract:** This paper presents an inductorless low power (LP) low noise amplifier (LNA) based on a Common Gate (CG) topology. The circuit combines gain boosting techniques to enable high gain LP LNA. The circuit is integrated in a 130nm CMOS technology and shows 20dB gain with 4dB Noise Figure and -12dBm IIP3. The power consumption is 1.32mW from a 1.2V supply.

#### Monday, 6 June 2011 2:20 PM Room 341-342 Session RMO3C: Devices and circuits for silicon based mm-Wave ICs Chair: Oren Eliezer, Xtendwave Co-Chair: Li-Wu Yang, Shanghai Jiao-Tong University

#### **RM03C-1** 2:20 PM 60GHz Antenna Integrated on High Resistivity Silicon Technologies Targeting WHDMI Applications

D. Titz<sup>1</sup>, R. Pilard<sup>2</sup>, F. Ferrero<sup>1</sup>, F. Gianesello<sup>2</sup>, D. Gloria<sup>2</sup>, C. Luxey<sup>1</sup>, P. Brachat<sup>3</sup>, G. Jacquemod<sup>1</sup>, <sup>1</sup>Université de Nice-Sophia-Antipolis, Valbonne, France, <sup>2</sup>ST Microelectronics, Crolles, France, <sup>3</sup>Orange Labs, La Turbie, France

**Abstract:** For the 60GHz market to flourish, low cost antennas and packages are required. In order to address these issues, we review in this paper achievable antenna performance using High Resistivity (HR) silicon technologies, discussing possible integration schemes, antenna design and 3D on wafer characterization. Antenna gain of 3.9dBi @ 60GHz has been measured making HR Si technology a promising one to address applications packaged in mm-Wave low cost technology.

#### **RMO3C-2 2:40 PM** A High-Isolation 60GHz CMOS Transmit/Receive Switch

C. Kuo<sup>1</sup>, H. Kuo<sup>1</sup>, H. Chuang<sup>1</sup>, C. Chen<sup>2</sup>, T. Huang<sup>1</sup>, <sup>1</sup>National Cheng Kung University, Tainan, Taiwan, <sup>2</sup>National University of Tainan, Taiman, Taiwan

**Abstract:** A 60GHz highly-isolation CMOS single-pole double-throw (SPDT) T/R switch fabricated with TSMC standard 90nm CMOS technology is presented. The leakage cancellation technique is used to increase the isolation between the transmitter and receiver ports. The measured results show the insertion loss is less than 3.5dB, and the isolation is higher than 28dB from 57-64GHz. The port isolation is higher than 34dB and the input 1dB compression point is 6.9dBm at 60GHz.

# RM03C-3 3:00 PM

# Integration of Antenna-on-Chip and Signal Detectors for Applications from RF to THz Frequency Range in SiGe Technology

S. Wane<sup>1</sup>, R. van Heijster<sup>2</sup>, S. Bardy<sup>1</sup>, <sup>1</sup>NXP-Semiconductors, Caen, France, <sup>2</sup>TNO Defence, Security and Safety, The Hague , Netherlands

**Abstract:** This paper presents design solutions for signal detectors and Antenna on-Chip (AoC) using a state-of-the-art SiGe technology. Both CML and CMOS detectors are designed, fabricated and compared in terms of their performances. AoC working at 60GHz, 77GHz, and 94GHz are designed and fabricated. Several AoC structures are proposed to experimentally evaluate bandwidth, near field coupling and radiation efficiency performances.AoC and SiGe Schottky diodes are characterized for THz applications.

#### **RM03C-4 3:20 PM** On-Chip Vertically Coiled Solenoid Inductors and Transformers for RF SoC Using 90nm CMOS Interconnect Technology

H. Namba, T. Hashimoto, M. Furumiya, Renesas Electronics Corporation, Kawasaki, Japan

**Abstract:** This paper presents very small on-chip vertically coiled solenoid inductors using 90nm CMOS interconnect technology. A variety of area-saving transformers without any additional processing steps are also presented: a solenoid overlaid with another inside-diameter solenoid, a solenoid coiled around another one, face-to-face solenoids. RF characteristics were evaluated based on S-parameter. Self-resonance frequencies resulted in higher than 40GHz, and coupling coefficients were larger than 0.7.

#### Monday, 6 June 2011 2:20 PM Room 343-344 Session RMO3D: mm-Wave VCOs Chair: Timothy Hancock, MIT Lincoln Laboratory Co-Chair: Fred Lee, SiTime

# RMO3D-12:20 PMA V-band Voltage Controlled Oscillator with Greater than 18GHz of<br/>Continuous Tuning range based on Orthogonal E mode and H mode control<br/>A. Jooyaie, F. Chang, University of California at Los Angeles, Los Angeles, United States

**Abstract:** A technique for wide continuous tuning range of Voltage Controlled Oscillators is presented. Technique relies on separate E and H mode excitation of resonator, avoiding the Q-degrading switches. The standing-wave VCO implemented in CMOS 65nm achieves a continuous tuning range from 58-76.2GHz, with an average phase noise of -89.5dBc/Hz at 1 MHz offset across the entire band, consumes an average of 5.8mW (excluding the output buffers), occupies 177 x177 µm and achieves a record FoM.

# **RM03D-2 2:40 PM** 118GHz fundamental VCO with 7.8% tuning range in 65nm CMOS

W. Volkaerts, M. Steyaert, P. Reynaert, Katholieke Universiteit Leuven, Leuven, Belgium

**Abstract:** This paper presents a 118GHz fundamental VCO in a 65nm low power CMOS technology. Using accumulation mode varactors, the oscillator covers a frequency range from 113.4GHz to 122.6GHz, which corresponds to a 7.8% tuning range. Combining with a variable supply voltage, the tuning range is extended to 11GHz (9.3%). The VCO draws 5.6mA from a 1V supply and the output is higher than -28.5dBm. The measured phase noise at 118.3GHz is -83.9dBc/Hz at 1MHz offset. The FOMT is -175.7dB.

## **RMO3D-3** 3:00 PM Fully Monolithic 18.7GHz 16ps GaAs Mode-Locked Oscillators

O. Yildirim, D. Ha, D. Ham, Harvard University, Cambridge, United States

**Abstract:** We report a mode-locked electrical oscillator fully integrated in GaAs. It self generates a periodic train of pulses with a 16ps pulse width and a 18.7GHz frequency. This is the fastest electrical mode-locked oscillator to date, and the first integration of reflective mode locked electrical oscillator. It works by sending a pulse back and forth on a coplanar waveguide with reflections at both ends. The reflection occurs with level-dependent gain that enables pulse formation and stabilization.

#### **RMO3D-4 3:20 PM** A 77GHz CMOS VCO with 11.3GHz Tuning Range, 6dBm Output Power, and Competitive Phase Noise in 65nm Bulk CMOS

V. P. Trivedi, K. To, W. Huang, Freescale Semiconductor, Inc., Tempe, United States

**Abstract:** We demonstrate, using a foundry-based 65nm bulk technology, mmWave CMOS VCOs in the range of 38GHz and 77GHz with highest reported continuous tuning range (14%-25%), competitive phase noise (-94dBc/Hz at 1MHz offset at 38GHz), and high Pout (6dBm) needed to readily integrate with CMOS PA and to tolerate PVT variations. Device and design optimizations responsible for the high performance are presented. The impact of temperature and VDD variation is reported for the first time.

#### Monday, 6 June 2011 4:00 PM Room 337-338 Session RMO4A: RF characterization and modeling of advanced CMOS

Chair: Bumman Kim, Pohang University of Science and Technology Co-Chair: Tzung-Yin Lee, Skyworks Solutions

#### RMO4A-1 4:00 PM Aging of 40nm MOSFET RF Parameters under RF conditions From Characterization to Compact Modeling for RF Design

L. Negre<sup>1</sup>, D. Roy<sup>1</sup>, F. Cacho<sup>1</sup>, P. Scheer<sup>1</sup>, S. Boret<sup>1</sup>, A. Zaka<sup>1</sup>, D. Gloria<sup>1</sup>, G. Ghibaudo<sup>2</sup>, <sup>1</sup>STMicroelectronics, Crolles, France, <sup>2</sup>Imep Lahc, Grenoble, France

**Abstract:** In the framework of MOSFET reliability for mixed-analog application, an investigation of RF parameters degradation is performed. An innovative flow, composed of DC and RF stress with DC and RF aging characterization, is presented. Degradation kinetics of main parameters are physically explained and modeled using PSP compact model to predict the behavior of stressed devices.

#### **RMO4A-2** 4:20 PM Small signal and HF Noise performance of 45nm CMOS technology in mm-Wave range

L. Poulain<sup>2</sup>, N. Waldhoff<sup>1</sup>, D. Gloria<sup>2</sup>, F. Danneville<sup>1</sup>, G. Dambrine<sup>1</sup>, <sup>1</sup>Institut d'Electronique de Microélectronique et de Nanotechnologie, Villeneuve d'Ascq, France, <sup>2</sup>STMicroelectronics, Crolles, France

**Abstract:** This paper aims to present DC, small signal and noise performance up mm-Wave range of 45-nm bulk CMOS Technology. S parameters were measured up to 67GHz, a HF noise model was extracted in 6-40GHz frequency range, and its accuracy verified through a comparison with the noise figure measured in W band. The technology offers fT, fMAX respectively of 200 and 300GHz in line with up-to-date published results for a 45nm CMOS Technology. A minimum noise figure of 4.5dB at 94GHz is demonstrated.

# RMO4A-3 4:40 PM

Analytical Model for RF Power Performance of Deeply Scaled CMOS Devices

U. Gogineni<sup>1</sup>, J. del Alamo<sup>1</sup>, A. Valdes-Garcia<sup>2</sup>, <sup>1</sup>Massachusetts Institute of Technology, Cambridge, United States, <sup>2</sup>IBM T.J Watson Research Center, Yorktown Heights, United States

**Abstract:** This paper presents a first order model for RF power of deeply scaled CMOS. The model highlights the role of device on-resistance in determining the maximum RF power. We show excellent agreement between the model and the measured data on 45nm CMOS devices across a wide range of device widths. The model allows circuit designers to quickly and accurately estimate the power and efficiency of a device layout without need for complicated compact models or simulations.

#### **RMO4A-4 5:00 PM** CMOS Digital Tunable Capacitance with tuning ratio up to 13 and 10dBm linearity for RF and mm-Wave Design

R. Debroucke<sup>1</sup>, A. Pottrain<sup>1</sup>, D. Titz<sup>3</sup>, F. Gianesello<sup>1</sup>, D. Gloria<sup>1</sup>, C. Luxey<sup>3</sup>, C. Gaquiere<sup>2</sup>, <sup>1</sup>STMicroelectronics, Crolles, France, <sup>2</sup>IEMN, Villeneuve d'ascq, France, <sup>3</sup>LEAT, Vallbone, France

**Abstract:** Capabilities offered by advanced silicon technologies enable both mm-Wave design and agile circuits development, then the development of high performance tunable capacitance is mandatory. This paper reviews the design, optimization and characterization of Digital Tunable Capacitance using STMicroelectronics BiCMOS 0.13µm technology. DTC with TWC architecture allows synthesized capacitance up to 110GHz, 10dBm P1dB and a tuning ratio equal to 13. Design of a 60GHz RTPS using 4 bits DTC is presented.

# Monday, 6 June 2011 4:00 PM Room 339-340 Session RMO4B: Integrated Front-End RFIC - LNA, Mixers, Filters Chair: Frank Henkel , IMST GmbH Co-Chair: Reynold Kagiwada, Northrop Grumman

#### **RMO4B-1** 4:00 PM A 280MHz CMOS Intra-symbol Intermittent RF Front End for Adaptive Power Reduction of Wireless Receivers

M. Nakamura, M. Ugajin, M. Harada, Nippon Telegraph and Telephone Corporation, Atsugi-shi, Japan

**Abstract:** For adaptive power reduction of wireless receivers, we developed the first intra-symbol intermittent (ISI) CMOS RF front-end. The LNA and mixer operate synchronously and intermittently within a single symbol-length. The experimental results of demodulation and the theoretical analysis of noise figure show the effectiveness of the ISI operation.

# **RMO4B-2** 4:20 PM A 7dB NF 60GHz-Band mm-Wave Transconductance Mixer

Y. Jin, J. R. Long, M. Spirito, Delft University of Technology, Delft, Netherlands

**Abstract:** A 60GHz-band doubly-balanced transconductance (Gm) mixer with an on-chip linear L-C combiner for RF and LO signal summation and impedance transformation is described. Class-AB biasing is employed for low quiescent dc power consumption ( $360\mu$ W at 1.2V). At fLO=58GHz and PLO=0dBm, the Gm-mixer prototype realizes 6.9dB DSB( $50\Omega$ ) NF, 6.2dB power conversion gain, -4.7dBm input-referred P-1dB, and +4.2dBm IIP3.

#### **RMO4B-3 4:40 PM** A 100-3000MHz, Up/Down-Convert, +29dBm IIP3, +13dB NF, Active Mixer with Integrated Fractional-N PLL and VCO

I. Fujimori-Chen<sup>1</sup>, B. Walker<sup>2</sup>, R. Broughton-Blanchard<sup>2</sup>, E. Balboni<sup>2</sup>, <sup>1</sup>Analog Devices, Inc., Somerset, United States, <sup>2</sup>Analog Devices, Inc., Wilmington, United States

**Abstract:** A broadband, high-dynamic range active mixer with integrated PLL and VCO is presented. The synthesizer uses a programmable fractional-N PLL with in-band phase noise FOM of -223dBc/Hz/Hz. The 100-3000MHz active mixer can be configured for up or down conversion. The mixer's linearity can be boosted from +25dBm to +29dBm, and optimized for a range of input frequencies. Designed in Si-Ge 0.25µm BiCMOS, the entire chip occupies 5.84 mm<sup>2</sup> and consumes 250mA from a 5V supply.

## **RMO4B-4 5:00 PM** A 1 to 5GHz Adjustable Active Polyphase Filter for LO Quadrature Generation

M. Kaltiokallio, J. Ryynänen, Aalto University, Espoo, Finland

**Abstract:** This paper focuses on the design of a highly tunable active polyphase filter with IRR better than 40dB. The active polyphase filter is implemented as a part of a simple RF receiver to demonstrate its feasibility for wide variety of wireless systems. The design consist of a high frequency adjustable gm-element that is optimized for active PPF. The filter achieves a tuning range of 1 to 5GHz while consuming supply current of 0.7 to 4.4mA. The silicon area of the filter is 64x85µm.

# Monday, 6 June 2011 4:00 PM Room 341-342 Session RMO4C: High performance CMOS Power Amplifiers Chair: Jyoti P. Mondal, Northrop Grumman Co-Chair: Leon van den Oever, Radio Semiconductor Corp.

## **RMO4C-1** 4:00 PM A 550-1050MHz +30dBm Class-E Power Amplifier in 65nm CMOS

R. Zhang<sup>1</sup>, M. Acar<sup>2</sup>, M. P. van der Heijden<sup>2</sup>, M. Apostolidou<sup>2</sup>, L. C. de Vreede<sup>1</sup>, D. M. Leenaerts<sup>2</sup>, <sup>1</sup>Delft University of Technology, Delft, Netherlands, <sup>2</sup>NXP Semiconductors, Eindhoven, Netherlands

**Abstract:** A 65nm CMOS broadband class-E PA using HV extended-drain devices is presented. To improve reliable operation, sub-optimum class-E operation is applied. The PA is followed by an off-chip two-stage LC ladder. The measurements show a DE 67% and a PAE 52% with a Pout 30dBm within 550-1050MHz. The output power variation is within 1.0dB and efficiency variation is less than 13%. The highest efficiency is observed at 700MHz with peak DE of 77% and peak PAE of 65% at a Pout of 31dBm.

#### **RMO4C-2** 4:20 PM Digital Polar Transmitter Using a Watt-Class Current-Mode Class-D CMOS Power Amplifier

T. Nakatani<sup>2</sup>, J. Rode<sup>3</sup>, D. F. Kimball<sup>4</sup>, L. E. Larson<sup>1</sup>, P. M. Asbeck<sup>1</sup>, <sup>1</sup>University of California, San Diego, La Jolla, United States, <sup>2</sup>Panasonic Corporation of North America, Cupertino, United States, <sup>3</sup>ZIVA Corporation, San Diego, United States, <sup>4</sup>MaXentric Technologies, LLC, San Diego, United States

**Abstract:** A digital polar transmitter with a watt-class CMOS power amplifier is demonstrated, implemented with a 0.15µm RF CMOS process. Current-mode class-D configuration and stacked FETs are used to obtain high efficiency and high breakdown voltage. The output stage is fed by a buck converter employing digital pulse width modulation with 47 MHz pulse rate. Overall efficiency of 26.5% efficiency was achieved while maintaining ACLRs within WCDMA specifications at 24dBm average output power.

# RMO4C-3 4:40 PM

# A Fully-Integrated K-band CMOS Power Amplifier with Psat of 23.8dBm, PAE of 25.1 %

Y. Kawano, T. Suzuki, A. Mineyama, M. Sato, T. Hirose, K. Joshin, Fujitsu Ltd., Atsugi, Japan

**Abstract:** A fully-integrated K-band power amplifier was designed and fabricated in standard 65nm CMOS process. The fabricated power amplifier shows the broadband characteristics which were the saturation power of more than 20dBm from 16-25GHz with the linear gain of more than 20dB. The peak value of the saturation power was 23.8dBm, and the power added efficiency (PAE) was 25.1% at 19GHz. The chip occupied area including the DC and RF pads is only 1.2x0.8mm.

#### **RMO4C-4 5:00 PM** A Fully-Integrated Efficient CMOS Inverse Class-D Power Amplifier for Digital Polar Transmitters

D. Chowdhury, S. V. Thyagarajan, L. Ye, E. Alon, A. M. Niknejad, University of California at Berkeley, Berkeley, United States