2009 IEEE Radio Frequency Integrated Circuits Symposium Boston, Massachusetts June 7-9, 2009

# PROGRAM

**Boston Convention and Exhibition Center**

Sponsored by IEEE Microwave Theory and Techniques Society IEEE Electron Devices Society and The IEEE Solid-State Circuits Society

#### **RFIC Plenary and Reception** Sunday Night (June 7, 2009)

After a busy day of outstanding RFIC Workshops (see page 10-55) the Plenary Session and RFIC Reception will be held on Sunday evening – June 7, 2009. These activities are the highlight of technical activities include the Plenary Session at 5:30pm in the Westin Boston Waterfront Hotel, Grand Ballroom A. The Plenary Session will include two outstanding speakers (See page 8-9) and the Student Paper Award ceremony. Immediately following the RFIC Plenary Session at 7:00pm is the RFIC Reception in the Westin Boston Waterfront Hotel, Grand Ballroom B &C. This social event is a key component of the RFIC Symposium, providing the opportunity to connect with old friends, make new acquaintances, and catch up on the wireless industry. Admittance is included with RFIC Symposium registration. Additional tickets can also be purchased separately at registration. The Reception is sponsored by the RFIC Steering Committee and Platinum Sponsors:

# cādence

### **RFIC Week Activities (June 6-10)**

#### Saturday June 6, 2009

02:00pm - 06:00pm Registration – BC&EC

#### Sunday June 7, 2009

07:00am - 06:00pmRegistration - BC&EC07:00am - 09:00amAttendee Breakfast - BC&EC, Room 258AB08:00am - 05:00pmWorkshops and Tutorials - BC&EC05:30pm - 06:40pmRFIC Plenary - WBWH, Grand Ballroom A07:00pm - 09:00pmRFIC Reception - WBWH, Grand Ballroom B & C

#### Monday June 8, 2009

| 07:00am - 05:00pm | Registration – BC&EC                      |

|-------------------|-------------------------------------------|

| 07:00am - 09:00am | Attendee Breakfast – BC&EC, Room 258AB    |

| 08:00am - 05:10pm | RFIC Technical Sessions (see pages 10-41) |

| 08:00am - 09:40am | RMO1A RMO1B RMO1C RMO1D                   |

| 10:10am - 11:50am | RMO2A RMO2B RMO2C RMO2D                   |

| 01:20pm - 03:00pm | RMO3A RMO3B RMO3C RMO3D                   |

| 03:30pm -05:10pm  | RMO4A RMO4B RMO4C RMO4D                   |

#### Tuesday June 9, 2009

07:00am - 05:00pmRegistration - BC&EC - BC&EC, Room TBD07:00am - 09:00amAttendee Breakfast - BC&EC, Room 253ABC08:00am - 04:00pmRFIC Oral and IF Technical Sessions (see pages 42-55)08:00am - 09:20amRTU1A RTU1B RTU1C10:20am - 11:40amIRTU2A, RTU2B, RTU2C01:20am - 02:40pmRTU3A RTU3B RTU3C02:00pm - 04:00pmRTU1F

This Program can be found on the RFIC website <u>http://www.rfic2009</u>. IMS sessions and exhibits are held on Tuesday - Thursday. IMS program can be found on the IMS website <u>www.ims2009.org</u>.

# **TABLE OF CONTENTS**

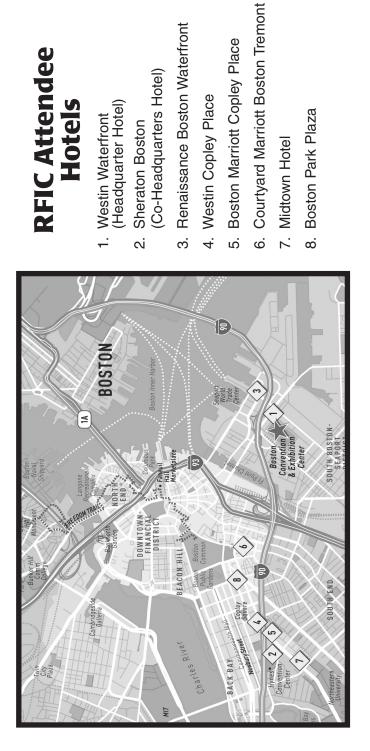

The RFIC Symposium will be held in Boston Massachusetts at the Boston Convention & Exhibition Center On June 7-9, 2009 in conjunction with the International Microwave Symposium. It opens Microwave week 2009, the largest RF/Microwave meeting of the year.

The RFIC Symposium brings focus to the technical accomplishments in RF Systems, circuit device, and packaging technologies for mobile phones, wireless communication systems, broadband access moderns, radar systems and intelligent transport systems.

| Table of Contents                                                                |          |  |

|----------------------------------------------------------------------------------|----------|--|

| Message from General Chair.                                                      |          |  |

| Message from Technical Program Chair                                             |          |  |

| Steering Committee                                                               |          |  |

| Advisory Board                                                                   |          |  |

| Executive Committee                                                              |          |  |

| Technical Program Committee                                                      |          |  |

| RFIC Schedule 2009                                                               | p.6-7    |  |

| Plenary Session.                                                                 | p. 7-9   |  |

| Session: RM01A: Cellular IC I                                                    | p. 10-11 |  |

| Session: RMO1B: Advanced Millimeter-Wave Circuits                                | p. 12-13 |  |

| Session: RM01C: Broadband IC I                                                   | p. 14-15 |  |

| Session: RM01D: Transformer Based VCOs                                           | p. 16-17 |  |

| Session: RMO2A: RFID and Low-Power Wireless Applications                         |          |  |

| Session: RMO2B: High-Frequency CMOS RF Receivers                                 |          |  |

| Session: RMO2C: PA Modulator Components                                          | p. 22-23 |  |

| Session: RMO2D: RF Modeling and Design Automation                                | p. 24-25 |  |

| Session: RMO3A: Cellular IC II                                                   | p. 26-27 |  |

| Session: RMO3B: 60-GHz Phased Arrays                                             |          |  |

| Session: RMO3C: Handset PA's & Concepts                                          |          |  |

| Session: RMO3D: Advanced VCO Topologies                                          | p. 32-33 |  |

| Session: RMO4A: WIAN and WiMax                                                   | p. 34-35 |  |

| Session: RMO4B: RF Front End Building Blocks                                     | p. 36-37 |  |

| Session: RMO4C: Frequency Generation Circuits: PLLs and Synthesizers             |          |  |

| Session: RMO4D: Submicron RFIC MOS and Novel Devices                             | p. 40-41 |  |

| Session: RTU1A: Broadband PA's and MIMO                                          | p. 42    |  |

| Session: RTU1B: New Ideas in CMOS RF Front-End Circuits                          |          |  |

| Session: RTU1C: Advanced Device Characterization and Non-Linear Circuit Analysis |          |  |

| Session: RTU2A: Wideband and Direct Digital Frequency Synthesizers               | p. 45    |  |

| Session: RTU2B: Millimeter-Wave Imaging and Communication Systems                | p. 46    |  |

| Session: RTU2C: Broadband IC II                                                  | p. 47    |  |

| Session: RTU3A: Millimeter-Wave VCOs                                             | p. 48    |  |

| Session: RTU3B: Integrated Filters for RF Applications                           | p. 49    |  |

| Session: RTU3C: On-wafer Wireless Testing and Passive RFIC Components            | p. 50    |  |

| Session: RTUIF: Interactive Forum                                                | p. 51-55 |  |

| Panel Sessions                                                                   | p. 56-58 |  |

| Workshops and Short Courses                                                      | p. 59-70 |  |

| Registration Information                                                         | p. 71-74 |  |

| Social Events.                                                                   | p. 75-76 |  |

| Guest Programs                                                                   |          |  |

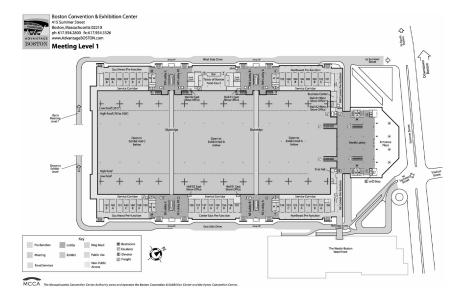

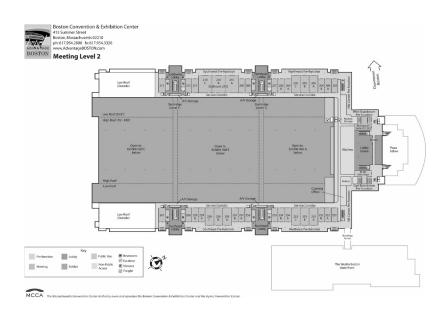

| BC&EC Floor Plans                                                                | p. 80    |  |

# **Message from the General Chair**

Tina Ouach

On behalf of the Steering Committee, I would like to welcome you to the RFIC Symposium!

The 2009 RFIC Symposium maintains its reputation as one of the foremost IEEE technical conferences dedicated to the latest innovations in RFIC development for wireless and wireline communication ICs. Running in conjunction with the International Microwave Symposium and Exhibition, the RFIC Symposium adds to the excitement of Microwave Week with three days focused exclusively on RFIC technology and innovation. The RFIC symposium will be held at the Boston Convention Center, June 7-9, 2009. The symposium begins on Sunday, June 7th with workshops targeted at RF technology, design, and system issues. The workshop organizers have put a strong emphasis in future RF integration, as well as a variety of

Power Amplifier designs including CMOS technology; advanced design techniques for mobile handsets and different solutions for PA and TX architectures. Don't miss out on this great opportunity to expand your horizons! Sunday evening activities continue at 5:30pm with RFIC Plenary Session at the Westin Water Front Hotel, Grand Ballroom A. Two renowned speakers will share their views on the direction and challenges that the RF IC industry will be facing. The first speaker, Christopher Snowden, Ph.D., Vice-Chancellor and Chief Executive of the University of Surrey, Guildford, UK, will discuss "Cost-effective Semiconductor Technologies for RF and Microwave Applications." The second speaker, George W. Everhart, CEO of Alien Technology Corporation, will cover "Real-world RFID deployments: What makes them work?" Following the Plenary Session, the RFIC Reception will be hosted in the Westin Water Front Hotel, Grand Ballroom B and C. This social event is a key component of the conference with the opportunity to connect with old friends and new acquaintances and catch up on the wireless industry.

The technical program includes oral sessions, an Interactive Forum (poster session), and two exciting lunch panel sessions. The oral presentation sessions start on Monday, June 8th with four parallel sessions of five papers per session throughout the morning and the afternoon. The oral sessions continue on Tuesday, June 9th with four papers per session and one hour break to synchronize with the IMS technical Program. The poster session will be held on Tuesday afternoon. The poster session is the perfect place to have an opportunity to have more detailed technical discussions with the authors. Panel Sessions are also planned at lunch time on Monday and Tuesday. The RFIC Symposium concludes on Tuesday allowing participants to attend the IMS and ARFTG as well as plenty of time to visit the exhibit hall.

The RFIC organization is thankful to the IMS2009 team, without whom we could not make this conference successful. Most of all, we are particularly thankful to all the technical contributors to the RFIC Symposium. We look forward to your participation. Please continue to make this conference so vibrant within the wireless industry!

I look forward to seeing you in Boston!

Tina Quach General Chair 2009 IEEE RFIC Symposium

# Message from the Technical Program Committee Chairs

David Ngo

Committee

has

diligently in selecting the best papers and assembling an excellent quality technical program this year. The symposium's main features include tutorial workshops, Plenary, Interactive Forum and several technical sessions. There will also be a student paper contest. The three best student papers will be selected by the Technical Program Committee and the awards will be presented in the Plenary Session. This year the RFIC Symposium begins on Sunday, June 7th with workshops at the advanced and tutorial level addressing RF technology, design and integration, at both system and circuit levels. The Plenary Session will be held on Sunday evening, following the workshops. The RFIC Reception will follow immediately after the plenary session, providing a relaxing time for all to mingle with old friends and catch up on the latest news. In addition to the technical sessions on Monday and Tuesday, the RFIC Symposium also features two exciting panel sessions and many workshops. Monday's lunch panel session entitled "Who will win the battle for the gigabit wireless in your home: Wireless HD, 802.11n, Wireless USB, or UWB?" has panelists from both industry and academia debating the future of high data rate wireless networks. Tuesday's lunch panel session, "60GHz CMOS radio: reality or fiction?" is posed to stimulate interactive discussions with the audience. The workshops on Sunday cover a wide range of topics from system to device technologies.

The interest in RFIC technology, and the venue offered by the Symposium to showcase the latest advancements, continues to make the RFIC Symposium the venue of choice for both industry and academia to meet, discuss results and exchange ideas. The 2009 RFIC Technical Program Committee will keep working tirelessly toward the goal of strengthening the technical quality and scope of the program, while maintaining and improving the legacy left by the previous Symposia. This would not be possible without holding the interest of professionals like you and gaining the trust of all the authors who submitted their work to the RFIC Symposium.

We hope you enjoy the 2009 RFIC Symposium!

Yann Deval and David Ngo Technical Program Chairs 2009 IEEE RFIC Symposium

On behalf of the Technical Program Committee, welcome to the 2009 IEEE Radio Frequency Integrated Circuits (RFIC) Symposium. This is a leading-edge IEEE technical conference dedicated to the advancement of integrated circuits and sub-systems for RE wireless. broadband communications, and many other emerging applications. The RFIC Technical Program worked

# **Steering Committee**

Tina Quach, Freescale Semiconductor Inc., *General Chair* Yann Deval, Univ. of Bordeaux, IMS Labs, *TPC Chair* David Ngo, RFMD, *TPC Co-Chair* Jacques C. Rudell, Univ. of Washington, *Finance Chai*r Bertan Bakkaloglu, Arizona State Univ., *Workshops Chair* Kevin McCarthy, Univ. College Cork, *Digest & CD ROM Chair* Albert Jerng, Ralink, *Publicity Chair* Yuhua Cheng, SHRIME Peking Univ., *Panel Sessions Chair* Albert Wang, UC Riverside, *Transactions/Guest Editor* Kevin Kobayashi, RFMD, *Student Papers Chair* Brian Floyd, IBM, *Secretary* Noriharu Suematsu, Mitsubishi Electric, *Asia Pacific Liaisons* Luciano Boglione, Univ. of Massachusetts, *IMS Liaisons* Takao Inoue, Univ. of Texas, Austin, *Webmaster*

Larry Whicker, LRW Associates, *Conference Coordinator*

# **Advisory Board**

Natalino Camilleri • Fazal Ali • Eliot Cohen Reynold Kagiwada • Sayfe Kiaei • Louis Lou David Lovelace • Vijay Nair • Steve Lloyd

# **Executive Committee**

Joseph Staudinger • Stefan Heinen • Luciano Boglione Jenshan Lin • Tina Quach

# **SSCS** Liaison

Kenneth O

# **Technical Program Committee**

Fazal Ali, Qualcomm Walid Ali-Ahmad, MediaTek Singapore Kirk Ashby, Microtune, Inc. Bertan Bakkaloglu, Arizona State University Jean-Baptiste Begueret, University of Bordeaux, IMS Lab Didier Belot, ST Microelectronics Paul Blount, Custom MMIC Design Georg Boeck, TU Berlin, Microwave Engineering Luciano Boglione, University of Massachusetts Lowell Natalino Camilleri, Alien Technology Sudipto Chakraborty, Texas Instruments Glenn Chang, MaxLinear Jing-Hong Chen, Analog Devices Nick Cheng, Skyworks Solutions Yuhua Cheng, Shrime Peking University Stephen Dow, ON Semiconductor Brian Floyd, IBM T. J. Watson Research Center Raniit Gharpurey. University of Texas, Austin Aditya Gupta, Anadigics Timothy Hancock, MIT Lincoln Lab Andre Hanke. Infineon Technologies AG Stefan Heinen, Infineon Technologies AG Frank Henkel, IMST GmbH Tian-Wei Huang. National Taiwan University Stavros Iezekiel, University of Leeds Lars Jansson, Tumbledown Technical Inc. Albert Jerng, Ralink Waleed Khalil, Obio State University Jaber Khoja, Microtune, Inc. Sayfe Kiaei, Arizona State University, Connection One Bumman Kim, Pohang University of Science and Technology

Kevin Kobayashi, RF Micro Devices, Inc. Chang-Ho Lee, Samsung Domine Leenaerts, NXP Semiconductor Donald Y.C. Lie, Texas Tech. University Fujiang Lin, IME Singapore Jenshan Lin, University of Florida Louis Liu, Northrop Grumman Corporation Ting-Ping Liu, Winbond Electronics, Shanghai David Lovelace, ON Semiconductor Danilo Manstretta, University of Pavia Kevin McCarthy, University College Cork Srenik Mehta, Atheros Communications Jyoti Mondal, Freescale Semiconductor Inc. Stefano Pellerano, Intel Corporation Sanjay Raman, Virginia Tech Madhukar Reddy, MaxLinear Bill Redman-White, NXP Semiconductor Eli Reese, TriQuint Semiconductor Mark Roberto, Intel Corporation Francis Rotella. Peregrine Semiconductor Jacques Rudell, University of Washington Carlos Saavedra, Queen's University Walter, Canada Derek Shaeffer, Beceem Communications, Inc. Osama Shana'a, MediaTek Corporation Eddie Spears, RFMD Joseph Staudinger, Freescale Semiconductor Inc. Bob Stengel, Motorola Noriharu Suematsu, Mitsubishi Electric Julian Tham, Arda Technologies Bruce Thompson, Motorola Labs Freek van Straten. NXP Semiconductor Albert Wang, University of California, Riverside Patrick Yue. University of California, Santa Barbara Gary Zhang, Skyworks Solutions

# **RFIC Schedule 2009**

The RFIC Symposium will be held in Boston, MA in the Boston Convention & Exhibition Center (BC&EC). The headquarters hotel is the Westin which is adjacent to the BE&EC. The RFIC Plenary and Reception will be held on Sunday June 7 starting at 5:30pm.

The RFIC Symposium is held as part of Microwave week. The RFIC Symposium is followed by the IMS Symposium and Exhibition and by ARFTG. Attendees of RFIC are invited to attend the IMS Plenary Session which will be held on Monday evening, June 8, 2009.

### Saturday June 6 2009

02:00pm - 06:00pm Registration – BC&EC

#### Sunday June 7, 2009

| 07:00am - 06:00pm | Registration – BC&EC                                |

|-------------------|-----------------------------------------------------|

| 07:00am - 09:00am | Attendee Breakfast – BC&EC, Room 258AB              |

| 08:00am - 05:00pm | Workshops and Tutorials – BC&EC                     |

| 05:30pm - 06:40pm | RFIC Plenary – Westin Hotel, Grand Ballroom A       |

| 07:00pm - 09:00pm | RFIC Reception – Westin Hotel, Grand Ballroom B & C |

#### Monday June 8, 2009

| 07:00am - 05:00pm | Registration – BC&EC                      |

|-------------------|-------------------------------------------|

| 07:00am - 09:00am | Speakers Breakfast – BC&EC, Room TBD      |

| 07:00am - 09:00am | Attendee Breakfast – BC&EC, Room 253ABC   |

| 07:00am - 05:00pm | Speakers Prep Room – BC&EC, Room TBD      |

| 08:00am - 05:10pm | RFIC Technical Sessions (see pages 10-41) |

| 08:00am - 09:40am | RM01A, RM01B, RM01C, RM01D                |

| 09:40am - 10:10am | Break                                     |

| 10:10am - 11:50am | RMO2A, RMO2B, RMO2C, RMO2D                |

| 11:50am - 01:20pm | RFIC Panel and Lunch                      |

| 01:20pm - 03:00pm | RM03A, RM03B, RM03C, RM03D                |

| 03:00pm - 03:30pm | Break                                     |

| 03:30pm - 05:10pm | RM04A, RM04B, RM04C, RM04D                |

| 05:30pm-06:45pm   | IMS Plenary Session                       |

# **RFIC Schedule** (Continued)

#### Tuesday June 9, 2009

| 07:00am - 05:00pm | Registration – BC&EC, Room TBD              |

|-------------------|---------------------------------------------|

| 07:00am - 09:00am | Speakers Breakfast – BC&EC, Room TBD        |

| 07:00am - 09:00am | Attendee Breakfast – BC&EC, Room 253ABC     |

| 07:00am - 05:00pm | Speakers Prep Room – BC&EC, Room TBD        |

| 08:00am - 04:00pm | RFIC Oral and IF Sessions (see pages 42-55) |

| 08:00am - 09:20am | RTU1A, RTU1B, RTU1C                         |

| 09:20am - 10:20am | Break and IMS Exhibit                       |

| 10:20am - 11:40am | RTU2A, RTU2B, RTU2C                         |

| 11:40am - 01:20pm | RFIC and IMS Panels, and IMS Exhibit        |

| 01:20pm - 02:40pm | RTU3A, RTU3B, RTU3C                         |

| 02:00pm - 04:00pm | RTUIF                                       |

| 02:40pm - 03:40pm | Break and IMS Exhibits                      |

# **Plenary Schedule**

#### Sunday, June 7, 2009 05:30 PM Westin Hotel – Grand Ballroom A Session RSU5A: RFIC Plenary

#### Chair: Tina Quach, Freescale Semiconductor Inc. Session Co-Chairs: Yann Deval, University of Bordeaux, IMS Lab David Ngo, RFMD

- 05:30pm Welcome message from General and TPC Chairs, Announcement of Student Paper Awards

- 05:45pm **RSU5A-1:** Cost-Effective Semiconductor Techniques for RF and Microwave Applications, **Christopher M. Snowden**, Univ. of Surrey, UK

- 06:15pm **RSU5A-2:** Real World RFID Developments: What Makes them Work **George W. Everhart,** Allen Technology Corp.

# **Plenary Speaker 1:**

Christopher M. Snowden – Vice-Chancellor and Chief Executive, University of Surrey, Guildford. Surrey. UK

#### Cost-effective Semiconductor Technologies for RF and Microwave Applications

**Abstract:** Microwave systems designers have a wide choice of semiconductor technologies for applications up to 100 GHz. While there is a natural tendency to choose integrated silicon as the technology of choice for most RFIC applications below 2 GHz and for many applications at higher frequencies, there are many other options available which can offer cost-competitive and performance-enhancing solutions.

This presentation will examine the current state-of-the-art in microwave and RF semiconductor technologies set against economic pressures which demand the lowest cost solution while meeting technical performance requirements, reliability and reproducibility. The presentation will examine factors affecting the wafer cost or equivalent die cost for various microwave technologies and the significance of mask set costs for some choices. The need for high yields and larger diameter wafer technology to reduce die costs led to 6" (150mm) wafer diameters becoming an industry standard for compound semiconductors.

The presentation will conclude by offering some insight into emerging technologies and their potential performance advantages for microwave and RF applications.

#### About Christopher M. Snowden:

Christopher Snowden is Vice-Chancellor and Chief Executive of the University of Surrey, Guildford, UK and a microwave engineer with wide experience of the international microwave and semiconductor industry.

He is currently a non-executive Director of Intense Ltd, which designs and manufactures photonic products such as laser arrays for the professional printing industry. He is also an advisor to DMD Ltd and Filtronic plc. He has previous experience as a Non-Executive of several other technology companies.

Prior to his appointment at Surrey he was Chief Executive Officer of Filtronic ICS. He joined Filtronic plc in 1998 as Director of Technology before being promoted to Joint Chief Executive Officer in 1999.

Professor Snowden is a Member of the UK's Council of the Engineering and Physical Sciences Research Council, the UK's Engineering and Technology Board (ETB), the Defence Scientific Advisory Council, the Board of Universities UK (UUK), and Deputy-President of the Institute of Engineering and Technology. He is Vice-President of the Royal Academy of Engineering and Chair of the Engineering Policy Committee.

Professor Snowden is a Fellow of the Royal Society, Fellow of the Royal Academy of Engineering, Fellow of the IEEE, a Fellow of the IET and a Fellow of the City and Guilds Institute. He was awarded the Royal Academy of Engineering's Silver Medal in 2004 for his 'outstanding contributions to the microwave semiconductor industry'. He was a Distinguished Lecturer for the IEEE Electron Devices Society for seven years until 2005. He was awarded the 1999 Microwave Prize of the IEEE Microwave Theory and Techniques Society.

# **Plenary Speaker 2:**

George W. Everhart – Chief Executive Officer, Alien Technology Corporation

#### Real-world RFID Deployments: What Makes Them Work

**Abstract:** Although there have been a variety of RFID pilots that have failed to reach a full implementation, there have been many real-world deployments which have been fully deployed and are providing a strong improvement in efficiency and effectiveness, netting a sound ROI. This talk will site a couple of examples of these successful deployments and recount some characteristics, both technical and otherwise, that are critical for these successes. These examples will also provide insight as to some of the remaining challenges for broad industry adoption.

#### About George W. Everhart

George W. Everhart joined Alien in January 2007. Mr. Everhart has over 25 years of executive leadership experience with specific expertise in leading high growth phases of industry leading technology companies. Everhart has held CEO and sales and marketing executive positions with both small startup companies in emerging markets, and large multinational companies, experiencing a rapid pace of growth. He has extensive experience in global markets as well as the domestic U.S. market.

Everhart recently held CEO positions with early stage startup companies, SealedMedia and Onesecure, where he led successful company funding and expansion and established both companies as recognized leaders in their markets. Previously, Everhart was Sr.VP, Worldwide Sales & Service for 3COM Corporation, managing the Americas, Asia/Pacific, and EMEA (Europe, Middle East & Africa) business activities as well as the 1,000 person global service organization. Prior, Everhart was President & CEO, Fujitsu PC Corporation, where he led the company's market entry and rapid growth in the notebook PC business. Everhart also held a series of executive leadership positions with Apple Computer during the company's fast growth years, 1987-1996, including VP US Sales, VP & GM PC Business Division, and VP Business & Government Sales. Everhart's early career included marketing, sales, and business management positions with The Braegen Corporation and Memorex Corporation.

Mr. Everhart has been active in industry, government, and education associations as well holding both board and advisory positions. He was a member of the "Highway One Committee" to assist in the automation of Congress. He currently is a member of the Board of Fellows at Santa Clara University.

Mr. Everhart holds a Bachelors degree in Psychology, and a Masters degree in Business Administration from Santa Clara University.

#### Monday June 8, 2009 08:00 AM BC&EC - Room 204AB Session: RM01A: Cellular IC I Chair: Didier Belot, ST Microelectronics Co-Chair: Andre Hanke, Infineon

# RM01A-1 8:00 AM

# RF Receiver Front-End with +3dBm Out-of-Band IIP3 and 3.4dB NF in 45nm CMOS for 3G and Beyond

Naveen K. Yanduru\*, Danielle Griffith\*, Kah-Mun Low\*, Poras Balsara\*\* \*Texas Instruments Inc., Dallas, TX 75243, USA, \*\*The University of Texas at Dallas, Richardson, TX 75080, USA

**Abstract:** A receiver front-end in 45nm standard CMOS is presented. The receiver achieves WCDMA system performance without an inter-stage SAW filter. High out-of-band linearity is achieved by reducing the RF circuitry and filtering the blockers after direct conversion. For the receiver at 1.9GHz, a +3.1dBm IIP3 is achieved for blockers that are 40MHz and 80MHz away from the RF carrier. NF is 3.4dB, IIP2 is +51dBm and current is 19.5mA for I,Q paths. LO is provided using on chip VCO and quadrature divider.

# RM01A-2 8:20 AM

# A SAW-Less CDMA Receiver Front-End with Single-Ended LNA and

# Single-Balanced Mixer with 25% Duty-Cycle LO in 65nm CMOS

Himanshu Khatri\*, Li Liu\*\*, Tony Chang\*\*, Prasad S. Gudem\*\*, and Lawrence E. Larson\*, \*University of California San Diego, La Jolla, CA, 92093, USA, \*\*, Qualcomm Inc., San Diego, CA, 92121, USA

**Abstract:** A fully integrated SAW-less direct conversion CDMA receiver with singleended LNA and modifed single-balanced passive mixer is manufactured in a 65 nm digital CMOS process. The measured receiver gain at 1.96 GHz was 37 dB, NF was 3 dB, IIP2 was (TB) was 65 dB.

#### **RMO1A-3 8:40 AM** A 0.13-μm CMOS Multi-Band WCDMA/HSDPA Receiver Adopting Silicon Area Reducing Techniques

Hyunwon Moon, Juyoung Han\*, Seung-Il Choi, Dongjin Keum\*, Byeong-Ha Park MSC Design Team, System LSI, Samsung Electronics, Korea, \*RF Development Team, System LSI, Samsung Electronics, Korea

**Abstract:** A multi-band WCDMA/HSDPA direct-conversion receiver to cover all six 3GPP bands is implemented in a 0.13 $\mu$ m CMOS process. The proposed integrated inductor structure and the mixed-type DC offset correction technique are very useful to reduce the increase of ilicon area generated by realizing a multi-band multi-mode RF transceiver. The measured full-path receiver performance is NF of <3dB, IIP3 of >-17dBm, and IIP2 of >+30dBm for all six bands. The current consumption is about 45mA at 2.8V supply.

# RM01A-4 9:00 AM

# A Tunable 300-800MHz RF-Sampling Receiver Achieving 60dB Harmonic Rejection and 0.8dB Minimum NF in 65nm CMOS

Z. Ru, E. Klumperink, C. Saavedra\*, B. Nauta University of Twente, Netherlands, \*Queen's University, Canada

**Abstract:** A 300-800MHz CMOS radio receiver aiming at software-defined radio is proposed. It exploits an LNA preceded by a tunable LC filter with one external coil to achieve voltage amplification for low NF and low-pass filtering to improve the 3rd and 5th harmonic rejection of an RF-sampling receiver to >60dB. The balun-LNA provides partial IM3 compensation, to drive a wideband sampling downconverter. The measured gain is 22-28dB while NF ranges from 0.8-4.3dB. The core consumes 6mW and clock takes 12mW.

# RM01A-5 9:20 AM

# The First Experimental Demonstration of a SASP-based Full Software Radio Receiver

F. Rivet\*, Y. Deval\*, JB. Begueret\*, D. Dallet\*, P. Cathelin\*\*, D. Belot\*\* \*IMS Laboratory, 351 Cours de la Liberation, 33405 Talence Cedex, France, \*\*STMicroelectronics, Central R&D, 38926 Crolles Cedex, France

**Abstract:** This paper presents the principles of a Sampled Analog Signal Processor (SASP) dedicated to Software Radio mobile device. The SASP aims to select a spectral envelope of a RF signal among all RF signals. It processed analogically the RF signal spectrum. It replaces the classical mixing and filtering operations. It dramatically reduces the A/D conversion frequency from GHz to MHz frequencies. Design strategy, applications and for the very first time, measurements are presented.

#### Monday June 8, 2009 08:00 AM BC&EC - Room 205A Session: RMO1B: Advanced Millimeter-Wave Circuits

Chair: Paul Blount, Custom MMIC Design Services Co-Chair: Kevin Kobayashi, RFMD

#### **RMO1B-1** 8:00 AM Current Combining 60GHz CMOS Power Amplifiers M. Bohsali and A. M. Niknejad BWRC, University of California at Berkeley

**Abstract:** Two 60GHz power amplifiers are presented in standard 90nm CMOS using integrated power combining and matching networks. The power amplifiers incorporate 4-way/2-way power splitters and combiners into their matching networks rather than using separate structures, and achieve 1dB output power of 12.1/10.1 dBm and saturation output power of 14.2/11.6 dBm respectively with saturation efficiency of 18.1/17.7% respectively when operated with a 1V supply.

### **RM01B-2 8:20 AM** 60GHz 45nm PA for Linear OFDM Signal with Predistortion Correction achieving 6.1% PAE and -28dB EVM

E. Cohen\*, S. Ravid\*, D. Ritter\*\* \*Mobile Wireless Group, Intel Haifa, Israel, \*\*Electrical Engineering Technion, Haifa, Israel

**Abstract:** 45nm CMOS 60 GHz PA optimized for linear modulation with 6dbm saturated power and 13dB gain is presented when biased at 70uA/um. A maximum PAE of 19.4% 8dBm Psat and 18dB gain is achieved for 200uA/µm bias point . The PA was tested using a digital predistortion algorithm and OFDM packets, and achieved PAE of 6.1% with -28dB EVM and 9% with -20dB EVM at output powers of -2dBm and +1dBm respectively.

#### **RM01B-3 8:40 AM** 60GHz and 80GHz Wide Band Power Amplifier MMICs in 90nm CMOS Technology

N. Kurita, H. Kondoh Central Research Laboratory, Hitachi, Ltd., Japan

**Abstract:** 60GHz and 80GHz-band power amplifier (PA) MMICs have been developed on a standard 90nm CMOS technology for use in RF front-ends of wide-band, low-cost communication and/or radar systems. Two PAs have three- and five-stage single-ended architectures, respectively. Under 1.0V bias supply, they have achieved saturation powers Psat of 12.6dBm and 10.3dBm with linear gains of 10.0dB and 12.2dB, respectively, the highest P<sub>sats</sub> reported to our best knowledge.

# RM01B-4 9:00 AM

**Low-Loss 0.13-**µm CMOS 50-70 GHz SPDT and SP4T Switches Y. A. Atesal, B. Cetinoneri, G. M. Rebeiz, University of California, San Diego

**Abstract:** This paper presents 50-70 GHz tuned  $\lambda/4$  single-pole double-throw (SPDT) and single-pole four-throw (SP4T) switches in a 0.13µm CMOS process. High substrate resistance is used for low insertion loss. The SPDT and SP4T switches result in a measured insertion loss of 2.0 and 2.3 dB at 60 GHz, with an isolation of > 32 dB and > 22 dB, respectively. To our knowledge, this paper presents the lowest loss 60 GHz SPDT and SP4T switches and the highest isolation SPDT switch in any CMOS technology to-date.

# RM01B-5 9:20 AM

# A Tunable Flipflop Based Frequency Divider up to 113GHz in SiGe:C Bipolar Technology

S.Trotta\*, J. John\*\* \*Freescale Semiconductor Inc., Schatzbogen 7, D-81829 Munich, Germany, \*\*Freescale Semiconductor Inc., 2100 East Elliot Road, 85284, Tempe, AZ, USA

**Abstract:** We present a tunable flipflop based frequency divider designed in a 200GHz fT SiGe bipolar technology. A new technique for tuning the sensitivity of the divider in the frequency range of interest is presented. The new technique also allows increasing the maximum toggle frequency of the divider. The chip is operational from 60GHz up to the record frequency of 113GHz. At 125°C the maximum speed is 96GHz. At a 3.3V power supply, the circuit, including the output buffer, consumes 35mA.

# Monday June 8, 2009 08:00 AM BC&EC - Room 206AB Session: RMO1C: Broadband ICI Chair: Chris Rudell, Univ. of Washington

Co-Chair: Ranjit Gharpurey, Univ. of Texas, Austin

#### **RMO1C-1** 8:00 AM

A DC-102GHz Broadband Amplifier in 0.12µm SiGe BiCMOS Joohwa Kim and James F. Buckwalter, Department of Electrical and Computer Engineering, University of California, San Diego, CA, 92093, USA

**Abstract:** RM0-1 An ultra-wideband amplifier scheme is realized with two cascaded stages that are equalized for high-bandwidth and low gain ripple. The amplifier is implemented in a 0.12µm SiGe BiCMOS process and achieves a 3dB bandwidth of 102GHz. The gain is 10dB with less than 1.5dB gain-ripple and group-delay variation under +/- 6ps over the entire 3dB bandwidth. The chip occupies an area of 0.29mm<sup>2</sup> including the pads and consumes 73mW from a 2V supply.

#### **RM01C-2** 8:20 AM A 1.8mW Wideband 57dB $\Omega$ Transimpedance Amplifier in 0.13um CMOS

F. Aflatouni, H. Hashemi, Department of Electrical Engineering-Electrophysics, University of Southern California, Los Angeles, CA, USA

**Abstract:** In optical links for on-chip or chip to chip data transfer, system components should be designed to be low power while occupying small areas. This paper presents a low power transimpedance amplifier (TIA) that is suitable to operate up to 10Gb/s in presence of 370fF input capacitance. The 0.13µm CMOS TIA consumes 1.8mW to provide 57 dBohm transimpedance gain, while occupying 0.015 mm<sup>2</sup> area. The measured input referred current noise of the TIA is less than 30pA/sqrt(Hz) across 8 GHz.

#### **RM01C-3** 8:40 AM 1 - 10GHz Inductorless Receiver in 0.13µm CMOS

Liuchun Cai, Ramesh Harjani, University of Minnesota, Minneapolis, MN 55455

**Abstract:** We describe inductorless wideband radio receiver architecture from 1GHz to 10GHz. Two receiver RF frontends designs are presented and compared: a traditional inductor peaking LNA and mixer (IPLM) and a capacitive peaking LNA and mixer circuit (CPLM). Mea srement results indicate that CPLM has better linearity, comparable noise figure and uses only 17% more power. Silicon area for CPLM is only 22% of IPLM. Both designs can be mated with an inductorless PLL also shown here.

#### **RMO1C-4 9:00 AM** A 2Gbps RF-Correlation-Based Impulse-Radio UWB Transceiver Front-End in 130nm CMOS

L. Zhou, Z. Chen, C.-C. Wang, F. Tzeng, V. Jain, and P. Heydari, University of California, Irvine

**Abstract:** The design of a carrier-less RF-correlation-based IR-UWB TRX front-end in 130nm CMOS is presented. Timing synchronization and coherent demodulation are implemented directly in the RF domain, enabling energy-efficient wireless communication at Gb/s data rates. Occupying mm<sup>2</sup> chip area, the TRX achieves a maximum data rate of 2Gbps and an RX sensitivity of -64dBm with a BER of 10-5, while requiring only 51.5pJ/pulse in the TX mode and 72.9pJ/pulse in the RX mode.

# **RM01C-5** 9:20 AM A Multi-modulation Low-power FCC/EC-compliant IR-UWB RF

**Transmitter in 0.18-μm CMOS** D. Barras, G. von Bueren, W. Hirt\*, H. Jaeckel, Electronics Laboratory, Swiss Federal Institute of Technology (ETH Zurich), 8092 Zurich, Switzerland, \*IBM Research, Zurich Research

Laboratory, 8803 Rüschlikon, Switzerland

**Abstract:** A multi-modulation RF transmitter IC intended for Impulse-Radio UWB is presented. The modulation rates extend up to 10Mpulses/s for BFSK, 500Mchips/s for shaped BPSK bursts and 1Gchips/s for unshaped BPSK bursts. This PLL-based TX achieves a power consumption of 81pJ/chip. The generated RF signals have spurious-free PSD and comply with U.S. and European regulations.

#### Monday June 8, 2009 08:00 AM BC&EC - Room 203 Session: RMO1D: Transformer Based VCOs

Chair: Timothy Hancock, MIT Lincoln Laboratory Co-Chair: Tian-Wei Huang, National Taiwan University

# RMO1D-1 8:00 AM

A 24 GHz Low Power VCO With Transformer Feedback

C. A. Lin, J. L. Kuo, K. Y. Lin, H. Wang, Dept. of Electrical Engineering and Graduate Institute of Communication Engineering, National Taiwan University, Taipei, Taiwan

**Abstract:** A K-band low power VCO fabricated by 0.13µm CMOS technology is developed. By employing a NMOS cross-coupled pair with a transformer feedback, low phase noise under low dc power condition can be achieved at higher frequency. The VCO exhibits a 2.2 GHz frequency tuning range. The output power and the phase noise at 1 MHz offset are -10 dBm and -113 dBc/Hz, respectively. The dc power consumption is 0.6 V/3 mW. To author's knowledge, this performance achieves the best FOM in CMOS K- band VCOs.

# RM01D-2 8:20 AM

A 1.7-mW, 16.8% Frequency Tuning, 24-GHz Transformer-Based LC-VCO using 0.18- $\mu$ m CMOS Technology,

Y.-H. Kuo, J.-H. Tsai\*, T.-W. Huang, National Taiwan University, \*Yuan Ze University, Taiwan

**Abstract:** A low-power, wide-tuning-range voltage-controlled oscillator (VCO) using 0.18-µm CMOS technology is presented in this paper. The proposed transformer-based LC-VCO has 16.8% frequency tuning range without switching techniques. To achieve wide-tuning- range and low-power in the same time, the current-reused topology is selected to demonstrate a low-power consumption of 1.7 mW. The VCO oscillation frequency at 22.6 GHz has a phase noise of -95dBc/Hz at 1 MHz offset.

# RM01D-3 8:40 AM

# A 92.6% Tuning Range VCO Utilizing Simultaneously Controlling of Transformers and MOS Varactors in 0.13 $\mu m$ CMOS Technology

Y. Takigawa, H. Ohta, Q. Liu, S. Kurachi\*, N. Itoh\*, T. Yoshimasu, Waseda University, \* Toshiba Corporation, Japan

**Abstract:** A Novel resonant circuit consisting of transformer-based variable inductors and MOS varactors is proposed to implement an ultra-wideband VCO IC. The VCO exhibits a frequency tuning range as high as 92.6 % spanning from 1.2 GHz to 3.27 GHz by simultaneousl y controlling the variable inductors and MOS varactors with a single control voltage. The measured phase noises at 1 MHz offset from the carriers are -124 dBc at 1.2 GHz and - 120 dBc at 3.1 GHz, respectively.

#### **RMO1D-4 9:00 AM** 1.1 to 1.9GHz CMOS VCO for Tuner Application with Resistively Tuned Variable Inductor

S. J. Cheng, Y. Zheng\*, C. H. Heng, National University of Singapore, \*Institute of Microelectronics, Singapore

**Abstract:** A VCO is fabricated in 0.35µm CMOS technology for tuner application as a proof of concept for a novel method of resistively tuning the inductance of an LC VCO. By employing a transformer as inductor, L is varied by changing the secondary coil current using active resistors. This eliminates the need for using multiple inductors, resulting in large savings in area. It achieves a tuning range of 1.06 to 1.88GHz (56%) and phase noise of -116.1dBc/Hz. It draws about 6.8mA from a 3V supply.

# RM01D-5 9:20 AM

# An Ultra-Low-Power CMOS Complementary VCO Using Three-Coil Transformer Feedback

C.-K. Hsieh, K.-Y. Kao, and K.-Y. Lin, Graduate Institute of Communication Engineering and Department of Electrical Engineering, National Taiwan University, Taipei, Taiwan, 10617, R.O.C.

**Abstract:** A ultra-low-power VCO based on the complementary cross-coupled structure with the three-coil transformer feedback is proposed and realized in  $0.18\mu$ m CMOS. This VCO has a 1 MHz offset phase noise of -118.5 dBc/Hz and consumes only 0.66 mW dc consumption. The FOM of this VCO is better than -195 dBc/Hz form 8.09 to 8.42 GHz, and the highest FOM of -198.6 dBc/Hz occurs at 8.2 GHz. The chip size is 530x 430 $\mu$ m<sup>2</sup>.

#### Monday June 8, 2009 10:10 AM BC&EC - Room 204AB Session: RMO2A: RFID and Low-Power Wireless Applications

Chair: Natalino Camilleri, Alien Technology Co-Chair: Glenn Chang, MaxLinear

#### **RMO2A-1** 10:10 AM Software Configurable 5.8 GHz Radar Sensor Receiver Chip in 0.13µm CMOS for Non-contact Vital Sign Detection Changzhi Li, Xiaogang Yu, Dong Li, Lixin Ran, and Jenshan Lin, University of Florida, Zhejiang University

**Abstract:** A direct conversion 5.8 GHz radar sensor chip with 1GHz bandwidth was designed and fabricated. This radar sensor chip is software configurable to set the operation point and detection range for optimal performance. Important design issues for direct conversion on-contact vital sign detection sensors, such as the effect of baseband flicker noise and gain budget, have been discussed. Experiments have been performed successfully in lab environment to detect the vital signs of human subject.

### **RMO2A-2 10:30 AM** An Asymmetric RF Tagging IC for Ingestible Medication Compliance Capsules

H. Yu, C. M. Tang, R. Bashirullah, University of Florida, Gainesville, FL, USA

**Abstract:** An asymmetric RF tagging IC fabricated in 130nm CMOS is powered by low frequency AC signals inside biological equivalent phantom solutions to create externally detectable RF bursts in the 915MHz ISM band. Such a device can be attached to the outer surface of standard ingestible capsules as a cost-effective method for medication compliance monitoring.

# RM02A-3 10:50 AM

A Novel CMOS Transmitter Front-end for Mobile RFID Reader Tongqiang Gao, Jingchao Wang, Chun Zhang, Baoyong Chi, Zhihua Wang Tsinghua University, Department of Electronic Engineering, Beijing, China

**Abstract:** In this paper, design considerations are expatiated to a novel structure of transmitter front-end for mobile RFID reader with 0.18µm CMOS process. The transmitter front-end consists of an up-conversion mixer, a linear PA and a non-linear PA. Controlled by the reader's working status, the implemented transmitter can provide high efficient carrier or highly linear ASK-modulation data at separate period. Test results verify the feasibility of the transmitter scheme.

# RM02A-4 11:10 AM

# A RF Transceiver with Auto Signal Detection and Combined PGA/RSSI

#### in 0.18µm CMOS for V2.1 Bluetooth Applications

Wei-Yi Hu, Jia-Wei Lin, Kuo-Chi Tien\*, Yong-Hsiang Hsieh\*, Chao-Liang Chen\*, Hung-Ta Tso\*, Yi-Shun Shih\*, Shao-Chueh Hu\*, Sao-Jie Chen, National Taiwan University, \*MuChip Corp. Ltd.

**Abstract:** A RF front-end transceiver is implemented in 0.18µm CMOS for v2.1 Bluetooth application. All detections and calibrations are realized without baseband's feedback using an incoming GFSK signal detection, auto LNA gain mode selection and auto gain calibration with combined PGA/RSSI function. The DEVM performance of transmitter is less than 6% and a 7.5dB system NF is achieved in receiver. Continuous current consumption of RX and TX are 32mA and 42mA respectively from a 1.8V internal regulator.

# RM02A-5 11:30 AM

# An Ultra-Low-Power 868/915 MHz RF Transceiver for Wireless Sensor Network Applications

R. van Langevelde, M. van Elzakker, D. van Goor, H. Termeer, J. Moss\* and A.J. Davie, Philips Research Europe, Eindhoven, The Netherlands, \*Philips Research UK, Cambridge, United Kingdom

**Abstract:** This paper describes an ultra-low-power transceiver operating in the 868/915 MHz frequency band using binary FSK at 45 kbit/s data rate. It achieves -89 dBm receiver sensitivity and -6 dBm transmit output power while consuming 1.6 mA and 1.8 mA, respectively, from a 1.2 to 1.5 V supply. It is fabricated in 0.13µm CMOS occupying 1.5 mm<sup>2</sup>, and it uses only 4 external components. The transceiver offers a small form factor, low cost and low power solution for wireless sensor network applications.

### Monday June 8, 2009 10:10 AM BC&EC - Room 205A Session: RMO2B: High-Frequency CMOS RF Receivers Chair: Walid Ali-Ahmad, MediaTek

Co-Chair: Sayfe Kiaei, Arizona State University

# **RM02B-1** 10:10 AM Low-Voltage, Inductorless Folded Down-Conversion Mixer in

65nm CMOS for UWB Applications

S. K. Hampel, O. Schmitz, M. Tiebout\*, I. Rolfes, Leibniz Universität Hannover, Germany, \*Infineon Technologies Austria AG, Austria

**Abstract:** The paper presents a low-voltage down-conversion mixer in 65nm CMOS for UWB applications. The inductorless folded circuit topology provides a peak gain of 14.5dB with 1dBm LO power and an 3dB-bandwidth from 1 to 10.5GHz. The input compression is better than -16.5dBm with an oIP3 of 7dBm at 2GHz. The circuit provides a minimum DSB noise figure of 6.5dB with a flicker-noise corner frequency of 2MHz. The mixer draws 12mA DC current from a 1.2V supply voltage resulting in a power dissipation of 14.4mW.

# RM02B-2 10:30 AM

### A 14-GHz CMOS Receiver with Local Oscillator and IF Bandpass Filter for Satellite Applications

W. Chen, T. Copani, H. Barnaby, S. Kiaei, Connection One, Arizona State University, Tempe, AZ

**Abstract:** This paper presents a 14-GHz transformer-coupled receiver front-end with LO and IF band-pass filter for satellite applications. The monolithic transformer's parameters were optimized through theoretical analysis of the circuit performance. The system was fabricated in a 0.13µm CMOS process. The receiver conversion gain is 20dB and the NF is 7dB at 400-MHz IF frequency. The LO shows -112dBc/Hz@1MHz phase noise from a 14-GHz carrier. The IC draws 40 mA total current from a 1.2 V supply.

# RMO2B-3 10:50 AM

#### A Two-Channel Ku-Band BiCMOS Digital Beam-Forming Receiver for Polarization-Agile Phased-Array Applications

B. Cetinoneri, Y. A. Atesal, G. M. Rebeiz, University of California, San Diego

**Abstract:** A 15 GHz two-channel receiver in 0.18-µm SiGe BiCMOS process is presented for digital beam-forming applications. The receiver is based on a dual-down-conversion architecture and results in a channel gain of 47.1 dB at 15 GHz, a NF of 3.1 dB, and an OP1dB of -11 dBm. The channel-to-channel coupling is < -48 dB. The chip consumes 70 mA (3.3 V) per channel and is  $2.6x2.2 \text{ mm}^2$ , including pads. To our knowledge, this is the first high-performance Ku-band beam-forming chip in SiGe BiCMOS technology.

#### **RM02B-4** 11:10 AM High Performance CMOS Receiver for Local Positioning Systems

M. Krcmar, V. Subramanian, G. Boeck, Microwave Engineering Lab, Berlin Institute of Technology, Berlin, 10587, Germany

**Abstract:** A fully integrated CMOS receiver consisting of an LNA and a mixer has been designed and fabricated in IBM BiCMOS 7WL 180 nm technology. An on chip balun loading the second stage of the LNA was implemented as well for single to differential conversion. Excellent experimental results were demonstrated: a conversion gain (CG) of 28 dB, a noise figure (NF) of 3.3 dB and an input third order interceptionpoint (IIP3) of -11 dBm while consuming only 50 mW.

# RM02B-5 11:30 AM

#### A CMOS Ku-band Single-Conversion Low-Noise Block Front-End for Satellite Receivers

Z. Deng, J. Chen, J. Tsai, A. M. Niknejad, University of California at Berkeley, USA

**Abstract:** This paper presents a Ku-band single-conversion low-noise block front-end in a 0.18- $\mu$ m CMOS technology. The front- end down-converts the input signal from the Ku-band (10.5-13 GHz) to the L-band (0.75-2.25 GHz). The in-band noise figure is between 2.8 to 4.2 dB. It achieves a gain of 50 dB with -dB variation. The inband OIP3 is above 17 dBm and output 1-dB compression point is above 9 dBm. The front-end consumes total of 75 mA from a 1.8 V supply. The die area is 0.8 x 1.8mm<sup>2</sup>.

#### Monday June 8, 2009 10:10 AM BC&EC - Room 206AB Session: RMO2C: PA Modulator Components

Chair: Freek van Straten, NXP Semiconductors Co-Chair: Joseph Staudinger, Freescale Semiconductor Inc.

# RM02C-1 10:10 AM

# A Hybrid Envelope Modulator Using Feedforward Control for OFDM WLAN Polar Transmitter

C. Lee, C. Chen and S. Wu, STC, ITRI, Taiwan, R.O.C.

**Abstract:** This paper presents a feedforward control for hybrid envelope modulator for applications in 802.11g OFDM WLAN polar transmitter. The feedforward control is constituted by hysteresis comparator and duplicate-linear amplifier that possess low power dissipation. For achieving high speed and high efficiency, the hybrid envelope modulator combines with a linear amplifier and a switch amplifier.

# RM02C-2 10:30 AM

# A Spurious Emission Reduction Technique for Power Amplifiers Using Frequency Hopping DC-DC Converters

#### J.-H. Chen, P.-J. Liu\*, Y.-J. E. Chen

Department of Engineering Science and Ocean Engineering, National Taiwan University, Taipei, Taiwan, \*Graduate Institute of Electronics Engineering, Department of Electrical Engineering, National Taiwan University, Taipei, Taiwan

**Abstract:** This paper presents a spurious emission suppression technique for RF power amplifiers using frequency-hopping DC-DC converters. The frequency-hopping technique changes the switching frequency of the DC-DC converter dynamically and reduces the peak spur created by using a DC-DC converter with a radio frequency power amplifier. The use of this technique can also reduce the size of the external passive components used for reducing the ripple voltage of the DC-DC converter.

# RMO2C-3 10:50 AM

### A Highly-Linear Radio-Frequency Envelope Detector for Multi-Standard Operation

J. Cha, W. Woo\*, C. Cho\*, Y. Park\*, C.-H. Lee\*, H. Kim\*\*, and J. Laskar, Georgia Institute of Technology, \*Samsung Design Center, \*\*Samsung Electro-Mechanics

**Abstract:** A highly-linear RF envelope detector for amplitude modulation of multiple wireless standards is presented. The RF envelope detector employs a differential voltage-to-current converter and a current-mode full-wave rectifier to enhance linearity of output envelope signal. It is shown that the proposed RF envelope detector linearly tracks 5-MHz sine-wave envelope at 1.9-GHz RF carrier as well as WCDMA and WiMAX envelopes at 1.95 GHz and 2.4 GHz, respectively.

# RMO2C-4 11:10 AM

#### A 1.55 GHz to 2.45 GHz Center Frequency Continuous-Time Bandpass Delta-Sigma Modulator for Frequency Agile Transmitters

M. Schmidt, M. Grözing, S. Heck, I. Dettmann, M. Berroth, D. Wiegner\*, W. Templ\*, A. Pascht\*, University of Stuttgart, \*Alcatel-Lucent Bell Labs Stuttgart, Germany

**Abstract:** This paper presents a 4th order continuous-time bandpass delta-sigma modulator (CT-BPDSM) with a programmable center frequency ranging from 1.55 GHz to 2.45 GHz. The modulator is suited to be applied in multi-standard class-S power amplifiers. The circuitis implemented in a 200 GHz-fT SiGe-technology. The measured SNR at 2.2 GHz center frequency is 45.5 dB in a bandwidth of 20 MHz. The measured uplink UMTS-FDD ACLR of the modulator output signal is 48.4 dB in the first adjacent channel.

# RM02C-5 11:30 AM

### A 25-dBm High-Efficiency Digitally-Modulated SOI CMOS Power Amplifier for Multi-Standard RF Polar Transmitters

S. Pornpromlikit, J. Jeong\*, C. D. Presti, A. Scuderi\*\*, and P. M. Asbeck, University of California at San Diego, \*Kwangwoon University, \*\*STMicroelectronics, s.r.l., USA

**Abstract:** A digitally-modulated power amplifier (DPA) is demonstrated in a 0.13-µm SOI CMOS technology, to be used in a multi- standard RF polar transmitter. The amplitude modulation is done by digitally controlling the number of activated unit amplifiers whose currents are summed at the output. The measured DPA delivers a 24.9-dBm peak output power at 900 MHz with a maximum power efficiency of 62.7%. It also exhibits high-efficiency performance for other carrier frequencies with a reconfigured matching.

### Monday June 8, 2009 10:10 AM BC&EC - Room 203 Session: RMO2D: RF Modeling and Design Automation

Chair: Kevin McCarthy, University College Cork Co-Chair: Francis Rotella, Peregrine Semiconductor

# RMO2D-1 10:10 AM

Effect of Substrate Contact Shape and Placement on RF Characteristics of 45 nm Low Power CMOS Devices

Usha Gogineni, Hongmei Li\*, Susan Sweeney\*, Jing Wang\*\*, Basanth Jagannathan\*\*, Jesus del Alamo, Massachusetts Institute of Technology, Cambridge, MA, \*IBM Microelectronics, Essex Jct, VT, \*\*IBM Microelectronics, Hopewell Junction, NY

**Abstract:** The substrate resistance (Rsx) of 45nm CMOS devices shows a strong dependence on the distance between the device edge and substrate ring and also on the number of sides the device is surrounded by the contact ring. Unilateral gain is modulated by Rsx andgate-body capacitance at low to medium frequencies (< 20GHz) and by the Rsx to drain junction capacitance pole at mm wave frequencies. The impact of Rsx on fT, maximum available gain, high frequency noise and power characteristics. minimal.

# RMO2D-2 10:30 AM

Design and Modeling of Planar Transformer-based Silicon Integrated Passive Devices for Wireless Applications

C.-H. Huang, T.-C. Wei, T.-S. Horng, S.-M. Wu\*., J.-Y. Li\*\*, C.-C. Chen\*\*, C.-C. Wang\*\*\*, C.-T, Chiu\*\*\*, and C.-P. Hung\*\*\*, National Sun Yat-sen University, National University of Kaohsiung\*, ITRI\*\*, Advanced Semiconductor Engineering\*\*\*, Taiwan

**Abstract:** This paper presents design and modeling techniques for Above-IC silicon process integrated passive devices (IPDs) that can be stacked with RF chips in a highly integrated 3D IC for wireless applications. The research starts to study modeling techniques for highfficiency planar transformers as near 90%. Based upon the proposed and modeled high-efficiency planar transformers, this paper explores novel designs of various passive devices including baluns, bandpass filters and power combiners.

# RMO2D-3 10:50 AM

Characterisation and Macro-modeling of Patterned Micronic and Nano-Scale Dummy Metal-Fills in Integrated Circuits

S.Wane, D. Bajon\*, NXP Semiconductors Caen, France, \*ISAE/Toulouse University Toulouse, France

**Abstract:** A wideband characterization and macro-modeling of patterned micronic and nano-scale dummy metal-fill is presented and impacts of metal-fill topologies on electrical performances are investigated. The validity of the proposed macro-modeling methodology is demonstrated by comparison with high frequency measurement of test case structures including on-chip interconnects and RF inductive loops.Compact broadband SPICE models are derived using fully scalable closed-form semi-analytical expressions.

# RMO2D-4 11:10 AM

Mosaic Placement of Very High Density 3D Capacitors for Efficient Decoupling Functionality in the RF Domain

O. Tesson, F. Le Cornec, S. Jacqueline, NXP Semiconductors Caen, France

**Abstract:** A layout driven approach used to fill empty space within MCM, with 3D high density decoupling capacitors is proposed. In a first time, a description of the innovative 3D unit cell is done based on process considerations. Then the method including the whole design flow is described and validated with the help of specific test cases and RF characterization data up to 6 GHz. A physical model is also proposed and implemented in the flow in order to compare simulated and measured data.

#### **RM02D-5** 11:30 AM On Modeling Parasitic Control Loops in RF SoCs: RF Cross-Coupling and Spurious Analysis

K. Muhammad, Chih-Ming Hung, Hunsoo Choo, Erkin Cubukcu, Texas Instruments Inc., Dallas, TX 75243

We address the issue of design verification of single-chip RF SOCs in the presence of unintentional cross-couplings and leakages due to proximity of aggressors and victims. We extend a previously presented VHDL based simulation methodology to allow building complex RF SoCs based on behavioral models. This approach has been successfully applied to investigate system behavior in the presence of aggressing nodes that create parasitic control loops due to unintentional and undesirable couplings.

#### Monday June 8, 2009 01:20 PM BC&EC - Room 204AB Session: RMO3A: Cellular IC II

Chair: Jyoti P. Mondal, Freescale Semiconductor Inc. Co-Chair: Fazal Ali, Qualcomm

# RM03A-1 01:20 PM

# Asynchronous Modulator for Linearization and Switch-mode RF Power Amplifier Applications

T. Johnson, K. Mekechuk, D. Kelly, J. Lu, Pulsewave RF, Inc., USA

**Abstract:** An implementation of an asynchronous modulator which encodes a modulated RF signal into a two level pulse train is described. The modulator is designed for RF switch mode amplifier applications and feedback linearization using conventional linear power amplifiers. The modulator is implemented in 0.18µm SiGe BiCMOS and operates over a frequency range from 750 MHz to 2.2 GHz. Experimental results are shown for a power amplifier module where the modulator is configured in a feedback loop.

# RM03A-2 01:40 PM

#### A Low Power 100 MHz – 2.5 GHz Digital-to-Time Conversion Based Transmitter for Constant-Envelope Direct Digital Modulation

Bob Stengel, S. A. Talwalkar, Tom Gradishar, Gio Cafaro, Motorola, Inc., Plantation, FL

**Abstract:** This paper reports a flexible direct digital modulation based low power transmitter in 90 nm CMOS that supports constant- envelope modulation using phase or frequency modulation for carrier frequencies from 100 MHz to 2.5 GHz with power drain of 130 mW and area of 0.7 mm<sup>2</sup>. For 8-PSK modulation upto 20 M symbol/s the RMS phase error is less than 4 deg. GSM phase error at 800-900 MHz and 1900 MHz is less than 1 deg RMS. APCO-25 FSK error is less than 2% from 150-900 MHz.

# RM03A-3 02:00 PM

A 65nm CMOS Low-Noise Direct-Conversion Transmitter with Carrier Leakage Calibration for Low-Band EDGE Application S. F. Chen, Y. B. Lee, Eric Sun, B. J. Kuo, G. K. Dehng, MediaTek Inc., Taiwan.

**Abstract:** A low-noise EDGE transmitter implemented in a 65nm CMOS process using direct-conversion architecture for low-band application is presented. The transmitter consists of a programable-gain I/Q modulator, a frequency divider and a power director for carrier leakage calibration. The out-of-band noise at 20MHz offset is less than -163dBc/Hz. The carrier leakage after calibration can reach -50dBc. The design consumes 21mA at 1.5V supply and 40mA at 2.7V supply and is housed in a 40-pin CFN package.

#### **RMO3A-4** 02:20 PM A Low-Cost Quad-Band Single-Chip GSM/GPRS Radio in 90nm Digital CMOS

K. Muhammad, C.-M. Hung, D. Leipold, T. Mayhugh, I. Elahi, I. Deng, C. Fernando, M.-C. Lee, T. Murphy, J. L. Wallberg, R. B. Staszewski, S. Larson, T. Jung, P. Cruise, V. Roussel, S.K. Vemulapalli, R. Staszewski, O.E. Eliezer, G. Feygin, K. Kunz, K. Maggio, Texas Instruments Inc., Dallas, TX 75243

**Abstract:** We present a quad-band single-chip GSM/GPRS radio in 90nm digital CMOS process based on the Digital RF Processor technology. This chip integrates all functions from physical layer to the protocol stack and peripheral support in a single RF SoC. The transceiver exceeds all 3GPP specifications demonstrating a receive NF of 1.8 dB and a margin of 8dB on TX spectral mask at 400 KHz offset in GSM850/900 bands. The transceiver is best-in-class in area and occupies only 3.8 mm<sup>2</sup> of silicon area.

# RM03A-5 02:40 PM

# A Multi-band High Performance Single-chip Transceiver for WCDMA/HSDPA

C. S. Chiu\*, B. S. Heng\*\*, E. S. Khoo\*\*, S. R. Karri\*\*, B. J. Kuo\*, C. H. Shen\*, T. Y. Sin\*\*, C. Y. Wang\*, W. Yang\*\*, H. L. Zhang\*\*, Walid Y. Ali-Ahmad\*\*, C. L. Heng\*\*, G. K. Dehng\*, \*MediaTek Inc., Hsinchu, Taiwan, 300, R.O.C., \*\*MediaTek Singapore, Ayer Rajah, Crescent, Singapore 139964

**Abstract:** A multi-band single-chip RFIC has been implemented in 0.18µm SiGe BiCMOS process for WCDMA/HSDPA applications. The direct-conversion receiver achieves competitive system performance: -110.5dBm sensitivity, 20dB and 12dB blocking margin for ACS case 1 and case 2, respectively, and excellent in-band blocking margins. The direct-modulation transmitter achieves more than 90dB dynamic range, and excellent EVM performance: <3.5%. In Band I, the RX and TX sections draw each 35mA and 65mA, respectively.

#### Monday June 8, 2009 01:20 PM BC&EC - Room 205A Session: RMO3B: 60-GHz Phased Arrays Chair: Brian Floyd, IBM Co-Chair: Georg Boeck, TU-Berlin

#### **RMO3B-1 01:20 PM** A Bidirectional TX/RX Four Element Phased-array at 60GHz with RF-IF Conversion Block in 90nm CMOS Process E. Cohen\*, C. Jakobson\*, S. Ravid\*, D. Ritter\*\*, \* Mobile Wireless Group, Intel Haifa, Israel, \*\* Electrical Engineering Technion, Haifa, Israel

**Abstract:** A 60 GHz 4 element bidirectional phased-array TX/RX chip with a 2 bit phase shifter and IF converter to/from 12GHz, using 90nm CMOS process, is described. The array features 7 dB gain, measured NF of 9 dB, IP1dB of -19dbm for RX, and output Psat of +3.5dBm for TX, drawing 60 mA from a 1.3-V supply. The RMS amplitude and phase error of the phase shifter is 0.7dB and 2deg max respectively from 57 to 66 GHz. Total die area 1.6x1mm<sup>2</sup> with half of the area being the IF converter block.

#### **RM03B-2** 01:40 PM A 60GHz Digitally-Controlled RF-Beamforming Receiver Front-end in 65nm CMOS

Y.Yu, P.G.M. Baltus, A.J.M. de Graauw<sup>\*</sup>, E. van der Heijden<sup>\*</sup>, M. Collados<sup>\*</sup>, C. Vaucher<sup>\*</sup>, A.H.M. van Roermund, Eindhoven University of Technology, Eindhoven, The Netherlands; \*NXP Semiconductors, Research, Eindhoven, The Netherlands

**Abstract:** Phased arrays form a crucial step towards high data rate 60GHz wireless communication. This paper presents a fully integrated digitally controlled 60GHz RF-beamforming receiver front-end in CMOS. Using digitally controlled active phase shifters, each path of the scalable architecture achieves 10dB power gain, 7.2dB noise figure, a 360° phase shift range in 22.5° steps at 61GHz, and a 3dB-bandwidth of 5.4GHz, while only dissipating 78mW in each path. Chip area is 1.6mm<sup>2</sup>.

# **RMO3B-3 02:00 PM** A 60-GHz Band CMOS Phased Array Transmitter Utilizing Compact Baseband Phase Shifters

S. Kishimoto, N. Orihashi, Y. Hamada, M. Ito, K. Maruhashi, NEC Corporation, Japan

**Abstract:** A 60-GHz band phased array transmitter is developed based on 90-nm CMOS process featuring compact baseband phase shifters with ideally zero power consumption. The phase shifter changes an RF signal phase every 90 deg by switching baseband signal paths. The transmitter has 6 RF front-ends and 6 phase shifters to implement beam steering function for a 1 x 6 array antenna system. By controlling phase shifters, the beam steering from 0 deg to 60 deg is observed.

#### **RMO3B-4** 02:20 PM Embedded DiCAD Linear Phase Shifter for 57-65GHz Reconfigurable Direct Frequency Modulation in 90nm CMOS T. LaRocca, J. Liu, F. Wang, F. Chang, University of California at Los Angeles

**Abstract:** A digitally controlled artificial dielectric (DiCAD) differential transmission line is designed to perform agile linear phase shift over 100deg with thermometer-coded 16step control. It also operates with a 16 gain-step VGA to enable re-configurable and direct-frequency modulation at 60GHz with 256<sup>2</sup> states (1.1deg angular and 0.0007 magnitude resolutions) and -31dB static EVM for multiple PSK/QAM modulations. The modulator uses 0.33mm<sup>2</sup> core area in 90nm CMOS and consumes 10mA at 1V.

# RM03B-5 02:40 PM

# 60GHz Passive and Active RF-Path Phase Shifters in Silicon

Ming-Da Tsai, Arun Natarajan\* MediaTek Inc., Taiwan 300, R.O.C.,\*IBM T.J. Watson Research Center, New York 10598

**Abstract:** Integrated 60-GHz active and passive phase shifters for RF-path phase-shifting phased array transceivers are demonstrated in this paper. The active and passive phase shifters are based on vector-interpolation and reflection-type architecture, respectively. Measurements over process and temperature are also discussed and comparisons are drawn between active and passive phase shifting approach for 60GHz phased arrays.

#### Monday June 8, 2009 01:20 PM BC&EC - Room 206AB Session: RMO3C: Handset PA's & Concepts Chair: Nick Cheng, Skyworks Solutions Co-Chair: Eddy Spears, RF Micro Devices

# RM03C-1 01:20 PM

A Highly Efficient GSM/GPRS Quad-band CMOS PA Module C.-H. Lee, Y. Kim\*, J. J. Chang, K. S. Yang, K. H. An, I. Lee\*, K. Kim\*, J. Nam\*, H. Kim\*, Samsung Design Center, USA, \* Samsung Electro-Mechanics Corporation, Korea

**Abstract:** The highly efficient CMOS Power Amplifier Module (PAM) is designed for quad-band cellular handsets comprising GSM850, EGSM, DCS, PCS and supports Class 12 General Packet Radio Service (GPRS) multi-slot operation. This module integrates a power amplifier(PA) with a complete power control and protection in a standard RF CMOS process and also contains a high-Q integrated passive device (IPD) for an output-matching network guaranteeing high power-added efficiency (PAE).

### **RM03C-2** 01:40 PM Scalable CMOS Power Devices with 70% PAE and 1, 2 and 3.4 Watt Output Power at 2GHz

Mustafa Acar, Mark P. van der Heijden, Iouri Volokhine\*\*; Melina Apostolidou, Jan Sonsky\*\*, and Jan S. Vromans, NXP Semiconductors Research, Eindhoven, The Netherlands, \*\*, NXP-TSMC Research Center, Leuven, Belgium

**Abstract:** This paper reports RF power devices achieving 70% power-added efficiency (PAE) with 1, 2 and 3.4W output power at 2GHz. The power devices operate as sub-optimum class-E power amplifiers, having the advantage of 1.6 times higher output power with a slightly lower PAE than conventional class-E. The power devices use high voltage extended-drain NMOS (ED-NMOS) transistors in standard 65nm CMOS. A scalable lay-out design that we used preserves the high PAE for the various output power levels.

# RM03C-3 02:00 PM

### Asymmetric Multilevel Outphasing Architecture for Multi-standard Transmitters

SungWon Chung, Philip A. Godoy, Taylor W. Barton, Everest W. Huang, David J. Perreault, Joel L. Dawson, Massachusetts Institute of Technology, USA

**Abstract:** We describe a new outphasing transmitter architecture in which the supply voltage for each PA can switch among multiple levels. It is based on a new asymmetric multilevel outphasing (AMO) modulation technique which increases efficiency over a much wider output power range than the standard LINC system while maintaining high linearity. Simulations in 65nm CMOS show an efficiency improvement from 17.7% to 40.7% for HSUPA at 25.3dBm output power and from 11.3% to 35.5% for WLAN 802.11g at 22.8dBm.

#### **RM03C-4** 02:20 PM Distributed Power Amplifier with Electronic Harmonic Filtering

B. Thompson, B. Stengel, S. Olson, D. Scagmelli\*, A. Joseph\*, J. Dunn\*, Motorola Inc., \*IBM Microelectronics

**Abstract:** Providing all band power amplification and harmonic rejection are objectives with orthogonal implementations. This paper is a review of a new Distributed Power Amplifier (DPA) architecture using programmable frequency dispersion. This frequency domain dispersion is designed to achieve electronic harmonic filtering within the intended frequency band. Tunable reactive components are not practical in a high power transmitter network. Vector signal combining is used to provide harmonic filtering. RMO3C-5 This paper presents a new balanced architecture to improve the power added efficiency (PAE) of a 3G handset power amplifier without trading-off its stringent linearity requirement. It is modified from the structure of our Switched Load Insensitive Power Amplifier (LIPA®). Power amplifiers using the modified balanced structure retain the main features of the LIPA and provide boosted PAE performance in low and high power mode. The novel balanced structure is implemented into 4x4mm<sup>2</sup> power amplifier

# RM03C-5 02:40 PM

# Dual Mode Efficiency Enhanced Linear Power Amplifiers Using a

#### New Balanced Structure

Gary Zhang, Shiaw Chang, Sunny Chen and Jing Sun, Skyworks Solutions Inc, 5221 California Ave., Irvine, CA 92617 (Gary Zhang), 2427, W. Hillcrest Dr., Newbury Park, CA 91320, USA, (the rest)

**Abstract:** This paper presents a new balanced architecture to improve the power added efficiency (PAE) of a 3G handset power amplifier without trading-off its stringent linearity requirement. It is modified from the structure of our Switched Load Insensitive Power Amplifier (LIPA®). Power amplifiers using the modified balanced structure retain the main features of the LIPA and provide boosted PAE performance in low and high power mode. The novel balanced structure is implemented into 4x4mm<sup>2</sup> power amplifier.

#### Monday June 8, 2009 01:20 PM BC&EC - Room 203 Session: RMO3D: Advanced VCO Topologies

Chair: Waleed Khalil, Ohio State University Co-Chair: Timothy Hancock, MIT Lincoln Laboratory

#### **RM03D-1 01:20 PM** A Low-Power Dual-Band Oscillator Based on Band-Limited Negative Resistance

B. Catli, M. M. Hella, Rensselaer Polytechnic Institute

**Abstract:** This paper presents a 2.1/3.9 GHz oscillator in a GaAs technology. The dual band operation is based on switching the negative resistance bandwidth of a capacitive-ly degenerated common collector stage, while using a multi-resonant point tank, thus the band switching mechanism is moved to the active core of the oscillator. The measured phase noise for both bands is 136dBc/Hz@1MHz with a power consumption of 5.1mW, and a FOM of 195.39/-200.72 for 2.1/3.9GHz respectively.

#### **RM03D-2** 01:40 PM Low Phase Noise Gm-Boosted Differential Colpitts VCO with Suppressed AM-to-FM Conversion

J.P. Hong and S.G. Lee, Information and Communications University (ICU), Korea

**Abstract:** A gm-boosted differential Colpitts VCO is proposed, which allows lower oscillation start-up current and suppressed AM-to-FM conversion by the switching transistors. The proposed architecture allows wider range of saturation mode operation for the switching transistors which helps to suppress the AM-to-FM conversion. Measurement shows, at 1.84GHz(1.75~1.93 GHz), the phase noise of -105 and -128 dBc/Hz (FOM=191.2) at 100KHz and 1MHz offset, respectively, while dissipating 1.8 mA from 0.9-V supply.

### **RM03D-3 02:00 PM** An SoC with Automatic Bias Calibration of an RF Oscillator

Imran Bashir, R. Bogdan Staszewski, Oren Eliezer, Poras T. Balsara, Texas Instruments Inc., USA, University of Texas at Dallas, USA

**Abstract:** We present a novel scheme for calibrating RF oscillator current to ensure device reliability and improve performance of a wireless SoC. The proposed method calculates variance of the digitized phase error samples by a time-to-digital converter (TDC) in an all-digital phase-locked loop (ADPLL) to estimate oscillator noise as a function of the current setting. This concept is incorporated on a commercial single-chip radio SoC fabricated in 90-nm CMOS and is used in GSM/EDGE mobile handsets.

#### **RM03D-4** 02:20 PM A Low-Power, Small Area Quadrature LC-VCO Using Miniature 3D Solenoid Shaped Inductor

A. Tanabe, K. Hijioka, H. Nagase, Y. Hayashi, LSI Fundamental Res. Lab., NEC Electronics Corp., Japan

**Abstract:** A low-power, small area quadrature 5GHz LC-VCO includes 20GHz oscillator and 1/4 divider has been fabricated using miniature 3D solenoid shaped inductor in 90nm CMOS. Owing to the small area and small magnetic energy of the 3D inductor, small chip area of 2597mm<sup>2</sup> which is 1/10 of the reported smallest LC-VCOs and 2.8mW power consumption have been achieved without degrading Figure of Merit. This miniature LC-VCO is suitable for low-power, low-cost wireless transceivers and RF SoCs.

# RM03D-5 02:40 PM

### A Gate-Modulated CMOS LC Quadrature VCO

K.-W. Cheng and D. J. Allstot, University of Washington, Seattle, WA, USA

**Abstract:** A QVCO based on the time-varying gate-modulated coupling of two LC tank VCOs (GM-QVCO) is introduced. In addition to comparable phase noise performance, the GM-QVCO also exhibits superior quadrature phase accuracy, and suitability for low power supply voltage designs that use cascode current sources and active loads. It draws 2.4mA from a 1.8V power supply, displays a phase noise of -122dBc/Hz@1MHz offset, and has a quadrature phase error of 0.4°.

### Monday June 8, 2009 03:30 PM BC&EC - Room 204AB Session: RMO4A: WLAN and WiMax

Chair: Srenik Mehta, Atheros Communications Co-Chair: Julian Tham, Arda Technologies

# RMO4A-1 03:30 PM

Full Integrated 23dBm Transmit Chain With On-chip Power Amplifier and Balun for 802.11a Application in Standard 45nm CMOS process

A. A. Kidwai, A. Nazimov\*, Y. Eilat\*, O. Degani\*, Intel Corporation, Hillsboro OR, \*Intel Corporation, Haifa Israel

**Abstract:** A fully integrated transmit chain for 802.11a band with on-chip power amplifier and on-chip balun matching network in 45nm standard digital CMOS process demonstrates saturated power of +23dBm. The average efficiency is +5% and peak efficiency is +15%. A standalone class AB CMOS power amplifier with on-chip BALUN matching network was also produced and detailed characterization data is presented. Using digital predistortion, an EVM of -28dB is achieved at 19dBm for 5GHz band for standalone PA.

# RM04A-2 03:50 PM

# A Tri-Band MIMO Transceiver for Mobile WiMAX with an Image Rejection Ratio Tunable SSB Mixer

K. Oishi, D. Yamazaki, N. Hasegawa\*, N. Kobayashi\*, M. Kudo\*, T. Sasaki\*, S. Sakamoto\*\*, S. Yamaura, Fujitsu Laboratories Ltd., \*Fujitsu Microelectronics Ltd., \*\*Fujitsu Microelectronics Solutions Ltd., Japan

**Abstract:** A tri-band (2.3/2.5/3.5 GHz) MIMO transceiver for mobile WiMAX is presented. We adopted a double conversion transceiver that can switch lower and upper local modes to create an effective multiband transceiver. For the RX, the image rejection ratio (IRR) tunable single side-band (SSB) mixer was used to achieve over 50 dB IRR. The RCE for 2.5 GHz at -71.5 dBm input was below -28.7 dB and maximum input level up to -20 dBm was achieved. The TX had a dynamic range of over 56 dB.

## RMO4A-3 04:10 PM

#### Innovative Architecture for Dual-band WLAN and MIMO Front-end Module Based on a Single Pole Three Throw Switch-plexer

Chun-Wen Paul Huang, William Vaillancourt, Philip Antognetti, Tony Quaglietta, Mike McPartlin, Mark Doherty, and Christophe Masse, SiGe Semiconductor, Andover, MA 01810, USA

**Abstract:** An innovative architecture for a dual-band front-end module for WiFi / MIMO radios is presented. The FEM only consists of a dual-band PA and a SP3T switch-plexer. The switchplexer has a SP3T switch and an integrated Rx diplexer, which features 0.1 dB compression at > 33 dBm with <1 dB loss for Tx paths and < 2 dB loss with selectivity > 15 dB for Rx. These features reduce complexity and post PA loss of the FEM, resulting in 18 dBm with EVM < 3% and < -50 dBm/MHz harmonics in a 4 x 4 mm package.

### RM04A-4 04:30 PM

#### A Compact Low Power SDR receiver with 0.5-20MHz Baseband Sampled Filter

A. Geis\*, \*\* J. Ryckaert\*, J. Borremans\*, G. Vandersteen\*\*, Y. Rolain\*\*, J. Craninckx\*, \*IMEC, Belgium, \*\*Vrije Universiteit Brussels, Belgium

**Abstract:** A flexible low power receiver chain based on a wideband front-end in combination with a novel triangular-wave integration sampling baseband section, with strong embedded anti-alias protection, is proposed for multi-mode SDR receivers. The 90nm CMOS receiver operates from 200MHz up to 5.5GHz with a clock-tunable baseband bandwidth from 500kHz to 20MHz. It has 5.5 to 6dB NF, -0.9dBm IIP3 and 20 to 65dB of gain. Current consumption is 14.5mA from a 1.2V supply.

### **RMO4A-5 04:50 PM** Wi-Fi/WiMAX Dual Mode RF MMIC Front-end Module

P. H. Wu, S. M. Wang and M. W. Lee, Industrial Technology Research Institute, Taiwan

**Abstract:** A dual-mode RF front-end module is designed and implemented for Wi-Fi/WiMAX applications. It consists of a front-end MMIC and a dual-band power amplifier MMIC, both fabricated by  $0.5\mu$ m E/D-mode p-HEMT process. The front-end MMIC integrates a single-pole triple-throw antenna switch, two low noise amplifiers, a low pass filter and a diplexer in single chip. Overall module size is compact 7mm x 10mm, well tested with Wi-Fi/WiMAX OFDM signals

### Monday June 8, 2009 03:30 PM BC&EC - Room 205A Session: RMO4B: RF Front End Building Blocks

Chair: Osama Shana'a, MediaTek Co-Chair: Danilo Manstretta, University of Pavia

#### **RM04B-1 03:30 PM** A DC-to-22 GHz 8.4mW Compact Dual-feedback Wideband LNA in 90 nm Digital CMOS

M. Okushima\*, J. Borremans, D. Linten, G. Groeseneken, IMEC, Leuven, Belgium, \*currently at: Core Development Division, NEC Electronics corp., Japan