# 2019 IEEE Radio Frequency Integrated Circuits Symposium

Boston, Massachusetts, USA 2–4 June 2019

# PROGRAM

## **Boston Convention and Exhibition Center**

Sponsored by

IEEE Microwave Theory and Techniques Society IEEE Electron Devices Society and IEEE Solid-State Circuits Society

#### **RFIC Plenary, Reception, and Symposium Showcase**

#### Sunday Evening, 2 June 2019 Boston Conference and Exhibition Center

After a busy day immersed in RFIC Workshops, enjoy a relaxing evening with your RFIC colleagues at these special Sunday night RFIC events, to be held in the Boston Convention and Exhibition Center.

**17:30–19:00, Plenary Session, Ballroom:** The evening begins with the Student Paper Awards, Industry Paper Awards, and Tina Quach Service Award ceremony followed by two outstanding plenary speakers: Dr. Greg Henderson, Senior Vice President, Automotive, Communications and Aerospace/Defense at Analog Devices, and Dr. Ir. Michael Peeters, Program Director Connectivity and Humanized Technology at imec.

**19:00–21:00, RFIC Symposium Reception and Showcase, Ballroom Foyer:** Immediately following the Plenary Session is the RFIC Symposium Reception. Food and drinks will be provided while you connect with old friends, make new acquaintances and catch up on the latest developments in the field.

The RFIC Symposium Showcase is held concurrently with the reception and will feature our industry showcase and student paper finalists. The selected authors will be present to highlight their innovative work, summarized in poster format, and some will also show a live demonstration. The media will cover this event, making it an excellent opportunity to announce the latest RFIC developments and breakthroughs.

Admittance to all RFIC Sunday evening events is included with the RFIC Symposium registration and the Super-pass registration. Additionally, Sunday-night-only tickets can be purchased for those who cannot attend the rest of the RFIC Symposium but don't want to miss the microwave week's opening event. Please see <u>https://rfic-ieee.org/</u> for more details.

The RFIC Symposium Reception is made possible through the generous support of our corporate sponsors:

| June 2019)              |  |

|-------------------------|--|

| (1-4Jı                  |  |

| Schedule                |  |

| <b>RFIC Symposium S</b> |  |

# **Boston Conference and Exhibition Center**

| Event                                          | Location                  | Sat 1 June  | Sun 2 June       | Mon 3 June                 | Tue 4 June     |

|------------------------------------------------|---------------------------|-------------|------------------|----------------------------|----------------|

| Registration                                   | North Lobby               | 08:00-18:00 | 07:00-18:00      | 07:00-18:00                | 07:00-18:00    |

| Speakers' Breakfast                            | Room 210AB                |             |                  | 07:00-08:00                |                |

| Workshops & Short Courses                      | Rooms 150–161, 251–259B   |             | 08:00-<br>13:30- | 08:00–11:45<br>13:30–17:15 |                |

| Workshops Lunch                                | Room 210AB                |             | 11:45-           | 11:45-13:00                |                |

| Technical Lecture (includes lunch) Room 160ABC | Room 160ABC               |             | 11:45-13:15      |                            |                |

| Plenary Session                                | Ballroom                  |             | 17:30–19:00      |                            |                |

| Reception, Symposium Showcase                  | Ballroom Foyer            |             | 19:00-21:00      |                            |                |

| Interactive Forum                              | Room 253ABC               |             |                  |                            | 13:30–15:10    |

| Technical Sessions                             | Rooms 252AB, 254AB, 257AB |             |                  | 08:00-09:40<br>10:10-11:50 | 09:40<br>11:50 |

|                                                |                           |             |                  | $13:30-15:10\\15:55-17:15$ |                |

| Panel Sessions                                 | Room 162AB                |             |                  | 12:00-13:15                | -13:15         |

## **TABLE OF CONTENTS**

|        | Table of Contents                                                                                                                    |      |   |

|--------|--------------------------------------------------------------------------------------------------------------------------------------|------|---|

|        | Welcome Message from Chairs                                                                                                          |      |   |

|        | Steering Committee                                                                                                                   |      |   |

|        | Support Staff                                                                                                                        |      |   |

|        | Executive Committee                                                                                                                  |      |   |

|        | Advisory Board                                                                                                                       |      |   |

|        | Technical Program Committee                                                                                                          |      |   |

|        | RFIC 2019 Schedule                                                                                                                   |      |   |

|        | Plenary, Reception, and Symposium Showcase                                                                                           |      |   |

|        | Plenary Speakers<br>The Industry Showcase                                                                                            |      |   |

|        | The Student Paper Award Finalists Showcase                                                                                           |      |   |

|        | *                                                                                                                                    |      |   |

| AUNDAY | RMo1A: RF Receiver Building Blocks                                                                                                   |      |   |

|        | RMo1B: Advanced Devices, Characterization, and Modeling for Millimeter-Wave Applications                                             |      |   |

|        | RMo1C: Millimeter-Wave Radar and Imaging Systems                                                                                     |      |   |

|        | RMo2A: 5G and Millimeter-Wave Beamforming Building Blocks<br>RMo2B: Digitally Assisted Front-Ends for Emerging Wireless Applications | . 2  | 1 |

|        |                                                                                                                                      |      |   |

|        | RMo2C: RF-Inspired Emerging Technologies and Applications                                                                            |      | - |

|        | RMo3A: Millimeter-Wave Integrated Subsystems                                                                                         | 3    | 0 |

|        | RMo3B: Blocker Tolerance and Interference Cancellation                                                                               | 3.   | 5 |

|        | RMo3C: High-Performance Energy-Efficient Oscillators and Frequency Synthesizers                                                      |      |   |

|        | RMo4A: Millimeter-Wave PAs for 5G and Phased Arrays                                                                                  | . 3  | / |

|        | RMo4B: Receiver Circuits in CMOS-SOI Technology                                                                                      |      |   |

| _      | RMo4C: Mixed Signal Circuits for High Speed RF and Optical Transceivers                                                              |      |   |

| DAY    | RTu1E: Special Session: 5G Circuits and Systems<br>RTu1E: Energy-Efficient Wake-Up Receivers and IoT Transceivers                    | . 4  | 3 |

|        |                                                                                                                                      |      |   |

| ŝ      | RTu2E: Special Session: 5G Millimeter-Wave Beamforming Systems                                                                       | . 48 | 8 |

| -      | RTu2F: Broadband, Reconfigurable, and Multimode PAs and Transmitters                                                                 | . 5  | 0 |

|        | RTuIF: Interactive Forum                                                                                                             | . 5  | 2 |

|        | Panel Sessions                                                                                                                       | 5    | 6 |

|        | Technical Lecture                                                                                                                    | 5    | 8 |

|        | Workshops and Short Courses                                                                                                          | 5    | 9 |

|        | Social Events/Guest Program                                                                                                          |      |   |

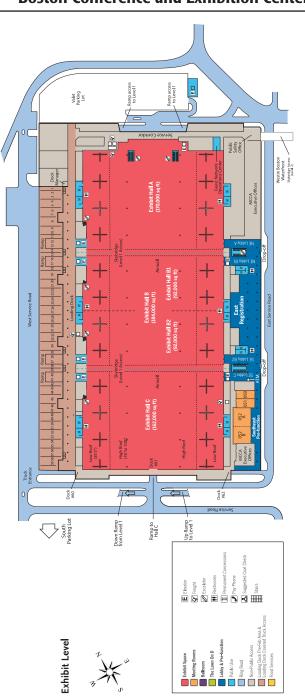

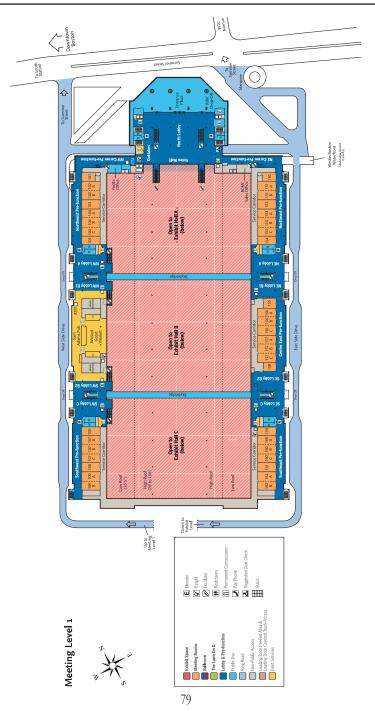

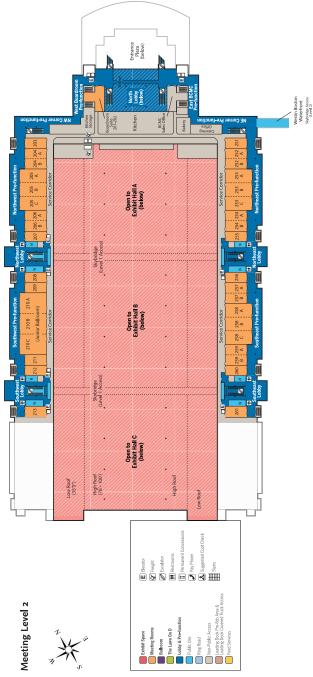

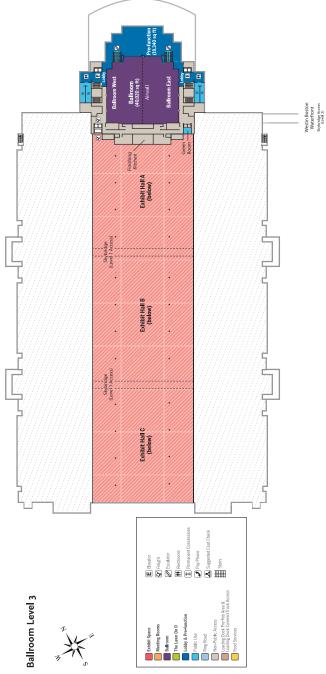

|        | Conference Venue Maps                                                                                                                | 78   | 8 |

#### Welcome Message from Chairs

We invite you to join us in the 2019 IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, to be held in Boston, Massachusetts, on 2–4 June 2019. The RFIC Symposium is the premier IC design conference focused exclusively on the latest advances in RF, Microwave and Millimeter-Wave integrated circuit (IC) technologies and designs, as well as innovations in high-frequency analog/mixed-signal ICs. This year the conference will also extend its focus to *emerging circuit technologies related to RFIC*, such as RF circuits and systems incorporating sensors and actuators, heterogeneous and 3D ICs, silicon photonics, quantum computing ICs, hardware security and machine learning applications, wearable and implantable systems, biomedical applications and autonomous systems like automotive and drones. It is with great pleasure that we cordially invite you to participate in this global event!

The RFIC Symposium is an annual IEEE conference that is combined with the International Microwave Symposium (IMS), ARFTG, and the Industry Exhibition to form the "*Microwave Week*", the world's largest RF/ microwave technical convention of the year. The 2019 Microwave Week will be held at the Boston Convention and Exhibition Center. Attendees will have the opportunity to interact with world experts, expand their network, and leave invigorated with new ideas and a drive to innovate.

RFIC 2019 features a very exciting and comprehensive program. In the evening of Sunday, 2 June 2019, the highlight during the RFIC Reception will be the popular *Interactive Symposium Showcase*, featuring poster presentations and demos of the most innovative and highly-rated industrial and academic papers.

To promote academic submissions, all of the RFIC student paper finalists will receive complimentary RFIC registration. Students may volunteer to help with RFIC (and/or IMS) conference logistics in exchange for complimentary conference registration, meals, T-shirts, and other benefits. *In addition, this year's student volunteers can buy the Super-pass at a discounted rate of \$250 and get access to all the sessions of IMS, RFIC and ARFTG!* The joint RFIC/IMS PhD Student Sponsorship Initiative Program will continue to involve selected first and second-year PhD students to complete technical assignments during the conference in exchange for complimentary conference registrations, lodging and meals.

The RFIC Symposium's educational program opens on Sunday, 2 June 2019, at 08:00 with 12 workshops covering the latest advances in a wide range of topics in RFIC technology and IC design, including power amplifiers, 5G systems, silicon photonics, quantum computing and hardware security. This year RFIC is also promoting a new educational experience for the attendees: a *Technical Lecture* comprising a 1 ½ hour interactive course delivered by a distinguished speaker during lunchtime on Sunday. For 2019, Prof. Ali Niknejad from University of California, Berkeley, will teach "*Fundamentals of mmWave IC Design in CMOS*". Admission is included with all RFIC Sunday workshops at no added cost, but don't forget to register early since seats will be limited to the first 250 registrants!

The RFIC Symposium's technical program opens with the RFIC Plenary Session on Sunday evening. The highlight of the plenary are two visionary talks by our distinguished plenary speakers. Dr. Greg Henderson, Senior Vice President, Automotive, Communications and Aerospace/Defense at Analog Devices, will discuss "*The Digital Future of RFICs*", describing how digitally-assisted-and-enabled RFICs are empowering the future of wireless sensing and communications with real world examples for applications like 5G and automotive radar. Dr. Ir. Michael Peeters, Program Director Connectivity and Humanized Technology at imec, will address the question "*Do the Networks of the Future Care About the Materials of the Past?*", taking a look at how the latest requirements for RFIC circuit design, new network capacity, reliability and latency can drive technology choices for the next 10 years. Additionally, at the plenary, we will present our annual awards for Students and Industry.

Immediately following the plenary session, we will have the 2019 RFIC Symposium Reception and Sboucase. During this engaging social and technical evening event supported by our corporate sponsors, industry showcase and student paper finalists will highlight their work in poster presentations and demonstrations. You will not want to miss the RFIC Reception and Showcase!

On Monday and Tuesday, the RFIC Symposium continues with multiple tracks of technical paper presentation sessions on several topics covering power amplifiers, phased arrays, advanced transceivers, imagers and radars, synthesizers and VCOs, IoT, RF and millimeter-wave front ends, semiconductors and emerging technologies. Two special sessions on 5G are scheduled on Tuesday morning and complement the 5G Summit technical sessions on Tuesday afternoon. The Interactive Forum session will be held in the afternoon on Tuesday.

Two enlightening panels will be featured during lunchtimes on both days. The Monday panel session titled "*The Internet of Things (IoT)* — *Back to the Future, or No Future?*" will feature experts from the industry and academia debating how the future IoT market will be affected by the accelerated introduction of 5G and the developments in 'big data' and artificial intelligence. On Tuesday, a joint IMS/RFIC panel titled "*Will Artificial Intelligence (AI) and Machine Learning (ML) Take Away My Job as an RF/Analog Designer?*" will feature distinguished panelists from academia, DARPA, CAD/EDA, and RF industries, debating the future of RF design and how we should prepare ourselves for the inevitable developments in design tools. Please make sure to bring your engaging opinions and questions to both panel sessions!

On behalf of the RFIC Steering and Executive Committees, we welcome you to join us at the 2019 RFIC Symposium in Boston, Massachusetts! Please visit the RFIC 2019 website (<u>https://rfic-ieee.org/</u>) for more details and updates.

General Chair Intel

**Waleed Khalil** TPC Chair The Ohio State University

**Brian Floyd** TPC Co-Chair North Carolina State University

#### **Steering Committee**

Stefano Pellerano, Intel, General Chair Waleed Khalil, The Ohio State University, TPC Chair Brian Floyd, North Carolina State University, TPC Co-Chair Nick Cheng, Skyworks Solutions, Publications Chair Oren Eliezer, PHAZR, RFIC Program Book Chair Gernot Hueber, Silicon Austria Labs, IMS Program Book Chair Mona Hella, Rensselaer Polytechnic Institute, Transactions Chair - JSSC Amin Arbabian, Stanford University, Transactions Chair - TMTT Mohyee Mikhemar, Broadcom, Session Organization Chair Andre Hanke, Intel, Publicity Chair Donald Y.C. Lie, Texas Tech University, Panel Sessions Chair Hua Wang, Georgia Tech, Workshop Chair Danilo Manstretta, Università di Pavia, Workshop Co-Chair Osama Shana'a, MediaTek, Student Papers Chair Hongtao Xu, Fudan University, Asia Pacific Liaison Francois Rivet, University of Bordeaux, European Liaison Domine Leenaerts, NXP Semiconductors, Industry Liaison Fred Lee, Verily Life Sciences, Secretary Steven Turner, BAE Systems, Submission Website Chair Michael Oakley, Raytheon, RFIC Website Chair Zaher Bardai, IMN Epiphany, VISA Letters

#### Support Staff

Elsie Vega, IEEE, Conference Manager Amanda Scacchitti, Publicity & Advisor Robert Alongi, IEEE, Finances Sandy Owens, MPA, Submissions Software George Vokalek, Causal Productions, Publications

#### **Executive Committee**

Bertan Bakkaloglu, *Arizona State University* Albert Wang, *University of California, Riverside* Kevin Kobayashi, *Qorvo* Walid Ali-Ahmad, *Facebook* Stefano Pellerano, *Intel*

#### **Advisory Board**

Jenshan Lin, University of Florida Stefan Heinen, RWTH Aachen University Joseph Staudinger, NXP Semiconductors Luciano Boglione, U.S. Naval Research Laboratory Natalino Camilleri, Nitero Yann Deval, University of Bordeaux David Ngo, Qorvo Jacques C. Rudell, University of Washington Lawrence Kushner, Raytheon

#### **Technical Program Committee**

Ehsan Afshari, University of Michigan Pietro Andreani, Lund University Amin Arbabian, Stanford University Edmund Balboni, Analog Devices Abdellatif Bellaouar, GLOBALFOUNDRIES Pierre Busson. STMicroelectronics Joseph Cali, BAE Systems Andreia Cathelin, STMicroelectronics Richard Chan. Finisar Nick Cheng, Skyworks Solutions Debopriyo Chowdhury, Broadcom Yuan-Hung Chung, MediaTek Foster Dai, Auburn University Oren Eliezer, PHAZR Kamran Entesari, Texas A&M University Ayman Fayed, The Obio State University Antoine Frappé, ISEN Lille Xiang Gao, Zhejiang University Vito Giannini, Uhnder Jane Gu, University of California, Davis Ping Gui, Southern Methodist University Ruonan Han, MIT Andre Hanke. Intel Ramesh Harjani, University of Minnesota Hossein Hashemi, University of Southern California Gary Hau, Qualcomm Hiva Hedayati, MACOM Mona Hella, Rensselaer Polytechnic Institute Gernot Hueber, Silicon Austria Labs Alvin Joseph, GLOBALFOUNDRIES Jennifer Kitchen, Arizona State University Eric Klumperink, University of Twente Harish Krishnaswamy, Columbia University

Oleh Krutko, Xilinx Timothy LaRocca, Northrop Grumman Fred Lee, Verily Life Sciences Domine Leenaerts. NXP Semiconductors Salvatore Levantino, Politecnico di Milano Donald Y.C. Lie, Texas Tech University Yao-Hong Liu, imec Danilo Manstretta, Università di Pavia Mohyee Mikhemar, Broadcom Omeed Momeni, University of California, Davis Arun Natarajan, Oregon State University Jevanandh Paramesh, Carnegie Mellon University Edward Preisler, TowerJazz Raja Pullela, MaxLinear Patrick Reynaert, Katholieke Universiteit Leuven Francois Rivet, University of Bordeaux Bodhisatwa Sadhu, IBM T.J. Watson Research Center Fabio Sebastiano, Technische Universiteit Delft Shahriar Shahramian. Nokia Bell Laboratories Osama Shana'a. MediaTek Margaret Szymanowski, NXP Semiconductors Leon van den Oever, Qualcomm Jeffrey S. Walling, Tyndall National Institute Hua Wang, Georgia Tech Ryan Wang, BAE Systems Yanjie Wang, Consultant David Wentzloff, University of Michigan Magnus Wiklund, Qualcomm Renaldi Winoto, Tectus Wanghua Wu, Samsung Haolu Xie, Transa Semiconductor Hongtao Xu, Fudan University

#### **RFIC 2019 Schedule**

#### **Boston Convention and Exhibition Center**

#### Saturday, 1 June 2019

08:00-18:00 Registration — North Lobby

#### Sunday, 2 June 2019

- 07:00–18:00 Registration North Lobby

- 07:00-08:00 Speakers' Breakfast --- Room 210AB

- 08:00–17:15 Workshops and Short Courses Rooms 150–161, 251–259B

- 09:40–10:10 Coffee Break Levels 1 & 2, East Side

- 11:45–13:00 Workshops Lunch Room 210AB

- 11:45–13:15 Technical Lecture Room 160ABC

- 15:10–15:40 Coffee Break Levels 1 & 2, East Side

- 17:30-19:00 RFIC Plenary Ballroom

- 19:00-21:00 RFIC Welcoming Reception Featuring RFIC Symposium Showcase Ballroom Foyer

#### Monday, 3 June 2019

- 07:00–18:00 Registration North Lobby

- 07:00-08:00 Speakers' Breakfast --- Room 210AB

- 08:00-17:15 Workshops and Short Courses Rooms 150-161, 251-259B

- 08:00–09:40 RMo1A Room 252AB: RF Receiver Building Blocks

- RMo1B Room 254AB: Advanced Devices, Characterization and Modeling for Millimeter-Wave Applications

- RMo1C Room 257AB: Millimeter-Wave Radar and Imaging Systems

- 09:40–10:10 Coffee Break Level 2, East Side

- 10:10–11:50 RMo2A Room 252AB: 5G and Millimeter-Wave Beamforming Building Blocks RMo2B — Room 254AB: Digitally Assisted Front-Ends for Emerging Wireless Applications

RMo2C — Room 257AB: *RF-Inspired Emerging Technologies and Applications* 11:45–13:00 Workshops Lunch — Room 210AB

- 12:00–13:15 RFIC Panel Session Room 162AB: *The Internet of Things (IoT) Back to the Future, or No Future?*

- 13:30–15:10 RMo3A Room 252AB: Millimeter-Wave Integrated Subsystems RMo3B — Room 254AB: Blocker Tolerance and Interference Cancellation RMo3C — Room 257AB: High-Performance Energy-Efficient Oscillators and Frequency Synthesizers

- 15:10–15:55 Coffee Break Level 2, East Side

- 15:55–17:15 RMo4A Room 252AB: *Millimeter-Wave PAs for 5G and Phased Arrays* RMo4B — Room 254AB: *Receiver Circuits in CMOS-SOI Technology* RMo4C — Room 257AB: *Mixed Signal Circuits for High Speed RF and Optical Transceivers*

#### Tuesday, 4 June 2019

- 07:00–18:00 Registration North Lobby

- 07:00-08:00 Speakers' Breakfast --- Room 210AB

- 08:00–09:40 RTu1E Room 252AB: Special Session: 5G Circuits and Systems

- RTu1F Room 254AB: Energy-Efficient Wake-Up Receivers and IoT Transceivers

- 09:40-10:10 Coffee Break Level 2, East Side

- 10:10–11:50 RTu2E Room 252AB: Special Session: 5G Millimeter-Wave Beamforming Systems RTu2F — Room 254AB: Broadband, Reconfigurable, and Multimode PAs and Transmitters

- 12:00–13:15 IMS/RFIC Joint Panel Session Room 162AB: Will Artificial Intelligence (AI) and Machine Learning (ML) Take Away my Job as an RF/Analog Designer?

- 13:30–15:10 Interactive Forum Room 253ABC

#### Plenary, Reception, and Symposium Showcase

#### Sunday Evening, 2 June 2019 Boston Convention and Exhibition Center

#### 17:30–19:00 RFIC Plenary Ballroom

#### Chair: Stefano Pellerano, Intel Co-Chair: Waleed Khalil, The Ohio State University

| 17:30 | Welcome Message from General Chair and TPC Chairs,                    |

|-------|-----------------------------------------------------------------------|

|       | Student Paper Awards, Industry Paper Awards, Tina Quach Service Award |

| 18:00 | The Digital Future of RFICs                                           |

|       | Dr. Greg Henderson, Analog Devices                                    |

| 18:30 | Do the Networks of the Future Care About the Materials of the Past?   |

|       | Dr. Ir. Michael Peeters, imec                                         |

#### 19:00-21:00

#### **RFIC Welcoming Reception**

#### Featuring Industry Showcase and Student Paper Awards Finalists Ballroom Foyer

The RFIC Interactive Reception starts immediately after the Plenary Session and will highlight the Industry Showcase and Student Paper Awards Finalists in an engaging social and technical evening event with food and drinks. Authors of these showcase and top student papers will present their innovative work, summarized in poster format. Some industry showcase papers will also offer live demonstrations. You will not want to miss the RFIC Reception! This event is supported by the RFIC Symposium corporate sponsors.

#### **Plenary Speaker 1**

Dr. Greg Henderson Senior Vice President Automotive, Communications and Aerospace & Defense Analog Devices

#### The Digital Future of RFICs

**Abstract:** Through significant advances in RFIC technology that have shrunk form factors and price points, high complexity RF, Microwave, and Millimeter wave solutions for communications and sensing are reaching the point of ubiquity. Large, complex multi-antenna and phased array solutions that previously only government organizations could justify have become the basis of modern wireless communications and automotive radar. Cars include millimeter-wave radar technology as a standard feature and 77GHz radar is playing a critical role in the autonomous vehicle revolution. Wireless bandwidth has grown from a trickle to a torrent and high channel count, multi-antenna systems are the key enabler for 5G, whose impact is predicted to extend beyond enabling that torrent of mobile data to revolutionizing industries as varied as agriculture, automotive, healthcare, and industrial.

To date, most of the advances in RFIC technology have largely been driven by the industry moving to high volume advanced geometry CMOS processes and massive increases in system-on-chip integration of complete antenna-to-bits signal chains. Since these are not the most friendly process technologies for traditional RF and microwave circuit blocks, the advances of tomorrow need new RF signal chain and circuit block architectures that exploit the strengths of advanced CMOS processes, while mitigating the disadvantages. This talk will show how such novel architectures and circuit innovations are enabled through leverage of high-performance digital capabilities, resulting in important performance advances that in fact exceed what could be obtained from traditional "RF friendly" process technologies. The talk will show how digitally-assisted-and-enabled RFICs are enabling the future of wireless sensing and communications with real world examples for applications like 5G and automotive radar.

#### About Dr. Greg Henderson

Dr. Greg Henderson was appointed Senior Vice President of Analog Devices' Automotive, Communications and Aerospace & Defense Group in 2017. Prior to this role, he served as vice president of the RF and Microwave business unit, responsible for the creation and execution of Analog Devices' strategy for its full suite of RF and microwave products and solutions.

Dr. Henderson has served in leadership roles in the microwave, semiconductor, and wireless communications industry for more than 20 years. Most recently, Dr. Henderson served as Vice President of the RF and Microwave business units of Hittite Microwave Corporation — prior to the acquisition by Analog Devices. From 2009 to 2013, Dr. Henderson served as the director of broadband products and later as the director of product management, for the Public Safety and Professional Communications Division of Harris Corporation. Prior to Harris Corporation, Dr. Henderson held various management and R&D/product development positions at TriQuint Semiconductor, IBM, and M/A-COM.

Dr. Henderson earned a B.S. in electrical engineering from Texas Tech University and was granted a Ph.D. in electrical engineering from the Georgia Institute of Technology. He holds seven patents in wireless communications and semiconductor technologies and has published over 20 conference and journal papers.

#### **Plenary Speaker 2**

#### Dr. Ir. Michael Peeters Program Director Connectivity+Humanized Technology imec

## Do the Networks of the Future Care About the Materials of the Past?

**Abstract:** The traffic in today's networks, 4G, 5G, mobile or otherwise, seems to be following nicely the exponential expectations projected each year. On the one hand, this is driven by and drives further CMOS scaling for the digital processing of information; on the other hand, this has pushed communication channels to use ever wider bandwidths. Unfortunately, not only the individual endpoint throughputs are increasing, but the amount of endpoints and their capabilities is skyrocketing as well. Moreover, capacity as a KPI is being complemented by reliability and latency as use-cases branch out beyond the traditional human-centric communications and entertainment into areas such as industrial automation, AR/VR and autonomous vehicles.

This is creating a perfect storm at the interface of the analog and digital worlds, where traditional scaling does not necessarily buy you performance; physical dimensions are dictated not by atom sizes but by quarterwavelengths of one kind or another; and speeds seem to all be converging at a point where switching frequencies venture far into the super-100GHz territory. For the first time in history, this is true for chip-to-chip, board-toboard, rack-to-rack, datacenter-to-datacenter, fiber and mobile wireless access systems.

Across the design space, this (finally!) has generated renewed interest into solution spaces that are less obvious, or were considered distinctly niche only a couple of years ago. We take a look at how we can tackle this, not only from an RFIC circuit design space, but also how new network capacity, reliability and latency requirements can drive technology choices for the next 10 years. This includes novel design and integration options for III-V, more exotic telluride and graphene approaches, but also dielectrics, ceramics and nanostructured materials.

#### About Dr. Ir. Michael Peeters

A passionate leader with a background in both research and strategy, Dr. Ir. Michael Peeters is Program Director Connectivity+Humanized Technology at imec. Michael has been identifying and implementing stateof-the-art technology opportunities in telecommunications through a career that spans two decades.

Both as Head of the Nokia Incubator and the Innovation Portfolio at Nokia, as well as CTO for the Wireless Division at Alcatel-Lucent, his role required him to make sense out of the uncertainty that exists when technological possibilities have to be balanced with business case realities. His team's responsibility: to see beyond the business analysis and help customers envision how emerging technologies and trends, such as 5G and AI, will impact their networks and end-user community.

Prior to his role as CTO for the Wireless Division, he was CTO for the Wireline Division. The team looked beyond the product roadmap and identified what new trends, technologies and tools were on the horizon and determined how those future opportunities fit into the Alcatel-Lucent pipeline. It was also during this period that the business commercialized VDSL2 Vectoring, an idea conceived 7 years earlier while leading the Bell Labs Access Nodes and DSL Technology department.

He has authored more than 100 peer-reviewed publications, many white papers and holds patents in the access and photonics domains. Michael earned a Ph.D. in Applied Physics and Photonics from Vrije Universiteit Brussel as well as a master's degree in Electrotechnical Engineering.

Outside of work, Michael is passionate about cooking and continues to refine the recipe for the perfect lasagna, balanced by bouts of long-distance running to offset the caloric intake inherent with such a quest.

#### Sunday, 2 June 2019

#### **BCEC Ballroom**

#### **The Industry Showcase**

#### Chair: Domine Leenaerts, NXP Semiconductors

The RFIC Industry Showcase Session, held concurrently with the plenary reception, will highlight the 10 outstanding paper finalists listed below, submitted by authors from the industry. In this interactive session, authors will present their innovative work in poster format, and some will also show a demonstration. These 10 paper finalists were nominated by the RFIC Technical Program Committee to enter the final contest and a committee of eleven judges have selected the top three among them after rigorous reviews and discussions. The top three will be announced during the RFIC Plenary Session preceding the Industry Showcase, and each winner will receive a plaque. This year's Industry Paper Award finalists are:

An 802. 11ba 495µW -92.6dBm-Sensitivity Blocker-Tolerant Wake-Up Radio Receiver Fully Integrated with Wi-Fi Transceiver <sup>1</sup>Intel, USA, <sup>2</sup>Intel, Mexico Renzhi Liu<sup>1</sup>, Asma Beevi K.T.<sup>1</sup>, Richard Dorrance<sup>1</sup>, Deepak Dasalukunte<sup>1</sup>, Mario A. Santana Lopez<sup>2</sup>, Vinod Kristem<sup>1</sup>, Shahrnaz Azizi<sup>1</sup>, Minyoung Park<sup>1</sup>, Brent R. Carlton<sup>1</sup>

- Reconfigurable 60-GHz Radar Transmitter SoC with Broadband Frequency Tripler in 45nm SOI CMOS IBM T.J. Watson Research Center, USA Wooram Lee, Tolga Dinc, Alberto Valdes-Garcia

- 22nm Fully-Depleted SOI High Frequency Noise Modeling up to 90GHz Enabling Ultra Low Noise Millimetre-Wave LNA Design

<sup>1</sup>GLOBALFOUNDRIES, Singapore, <sup>2</sup>GLOBALFOUNDRIES, USA, <sup>3</sup>Research Foundation CUNY, USA

L.H.K. Chan<sup>1</sup>, S.N. Ong<sup>1</sup>, W.L. Oo<sup>1</sup>, K.W.J. Chew<sup>1</sup>, Chi Zhang<sup>2</sup>, Abdellatif Bellaouar<sup>2</sup>, W.H. Chow<sup>1</sup>, T. Chen<sup>2</sup>, R. Rassel<sup>2</sup>, J.S. Wong<sup>1</sup>, C.K. Lim<sup>1</sup>, C.W.F. Wan<sup>1</sup>, J. Kim<sup>1</sup>, W.H. Seet<sup>1</sup>, David L. Harame<sup>3</sup>

A 26dBm 39GHz Power Amplifier with 26.6% PAE for 5G Applications in 28nm Bulk CMOS Intel, USA

Kaushik Dasgupta, Saeid Daneshgar, Chintan Thakkar, James Jaussi, Bryan Casper

Direct Digital Synthesizer with 14GS/s Sampling Rate Heterogeneously Integrated in InP HBT and GaN HEMT on CMOS

BAE Systems, USA

Steven Eugene Turner, Mark E. Stuenkel, Gary M. Madison, Justin A. Cartwright, Richard L. Harwood, Joseph D. Cali, Steve A. Chadwick, Michael Oh, John T. Matta, James M. Meredith, Justin M. Byrd, Lawrence J. Kushner

#### Excellent 22FDX Hot-Carrier Reliability for PA Applications

<sup>1</sup>GLOBALFOUNDRIES, USA, <sup>2</sup>GLOBÁLFOUNDRIES, Germany, <sup>3</sup>GLOBALFOUNDRIES, Singapore T. Chen<sup>1</sup>, Chi Zhang<sup>1</sup>, W. Arfaoui<sup>2</sup>, Abdellatif Bellaouar<sup>1</sup>, S. Embabi<sup>1</sup>, G. Bossu<sup>2</sup>, M. Siddabathula<sup>2</sup>, K.W.J. Chew<sup>3</sup>, S.N. Ong<sup>3</sup>, M. Mantravadi<sup>1</sup>, K. Barnett<sup>1</sup>, J. Bordelon<sup>1</sup>, R. Taylor<sup>1</sup>, S. Janardhanan<sup>1</sup>

#### Sunday, 2 June 2019

#### 19:00-21:00

#### **BCEC Ballroom Foyer**

A 1.04–4V, Digital-Intensive Dual-Mode BLE 5.0/IEEE 802.15.4 Transceiver SoC with Extended Range in 28nm CMOS <sup>1</sup>Samsung, Korea, <sup>2</sup>Samsung, USA

Nam-Seog Kim<sup>1</sup>, Myoung-Gyun Kim<sup>1</sup>, Ashutosh Verma<sup>2</sup>, Gyungseon Seol<sup>1</sup>, Shinwoong Kim<sup>1</sup>, Seokwon Lee<sup>1</sup>, Chilun Lo<sup>1</sup>, Jaeyeol Han<sup>1</sup>, Ikkyun Jo<sup>1</sup>, Chulho Kim<sup>1</sup>, Chih-Wei Yao<sup>2</sup>, Jongwoo Lee<sup>1</sup>

A High Efficiency 39GHz CMOS Cascode Power Amplifier for 5G Applications Samsung, Korea Hyun-chul Park, Byungjoon Park, Yunsung Cho, Jaehong Park, Jihoon Kim, Jeong Ho Lee, Juho Son, Kyu Hwan An, Sung-Gi Yang

- A Low Power Fully-Integrated 76–81GHz ADPLL for Automotive Radar Applications with 150MHz/µs FMCW Chirp Rate and -95dBc/Hz Phase Noise at 1MHz Offset in FDSOI <sup>1</sup>GLOBALFOUNDRIES, USA, <sup>2</sup>Mantric Technology, Canada Ahmed R. Fridi<sup>1</sup>, Chi Zhang<sup>1</sup>, Abdellatif Bellaouar<sup>1</sup>, Man Tran<sup>2</sup>

- X-Band NMOS and CMOS Cross-Coupled DCO's with a "Folded" Common-Mode Resonator Exhibiting 188.5dBc/Hz FoM with 29.5% Tuning Range in 16-nm CMOS FinFet Intel, Israel R. Levinger, D. Ben-Haim, I. Gertman, S. Bershansky, R. Levi, J. Kadry, G. Horovitz

<u>Industry Paper Contest Eligibility</u>: The first author must have an industry affiliation. The first author must also be the lead author of the paper and must present the paper at the symposium.

#### The Student Paper Award Finalists Showcase

#### Chair: Osama Shana'a, MediaTek

The RFIC Symposium's Student Paper Award is devised to encourage student paper submissions to the conference as well as to give the authors of the finalist papers a chance to promote their research work with the conference attendees after the plenary session during the reception time. Twelve outstanding student paper finalists were nominated this year by the RFIC Technical Program Committee to enter the final contest. A committee of eleven judges selected the top three papers after rigorous reviews and discussions. All finalists benefit from a complimentary RFIC registration. The top three Student Papers will be announced during the RFIC Plenary Session, and each winner will receive an honorarium and a plaque. This year's Student Paper Award finalists are:

A 4×4×4-mm3 Fully Integrated Sensor-to-Sensor Radio Using Carrier Frequency Interlocking IF Receiver with -94dBm Sensitivity

Li-Xuan Chuo<sup>1</sup>, Yejoong Kim<sup>1</sup>, Nikolaos Chiotellis<sup>1</sup>, Makoto Yasuda<sup>2</sup>, Satoru Miyoshi<sup>3</sup>, Masaru Kawaminami<sup>2</sup>, Anthony Grbic<sup>1</sup>, David Wentzloff<sup>1</sup>, Hun-Seok Kim<sup>1</sup>, David Blaauw<sup>1</sup> <sup>1</sup>University of Michigan, USA, <sup>2</sup>Mie Fujitsu Semiconductor, Japan, <sup>3</sup>Fujitsu Electronics, USA

A 24–43GHz LNA with 3.1–3.7dB Noise Figure and Embedded 3-Pole Elliptic High-Pass Response for 5G Applications in 22nm FDSOI Li Gao, Gabriel M. Rebeiz University of California, San Diego, USA

A 77dB-SFDR Multi-Phase-Sampling 16-Element Digital Beamformer with 64 4GS/s 100MHz-BW Continuous-Time Band-Pass ΔΣ ADCs Rundao Lu, Sunmin Jang, Yun Hao, Michael P. Flynn University of Michigan, USA

A Sub-mW All-Passive RF Front End with Implicit Capacitive Stacking Achieving 13dB Gain, 5dB NF and +25dBm OOB-IIP3 Vijaya Kumar Purushothaman, Eric Klumperink, Berta Trullas Clavera, Bram Nauta University of Twente, The Netherlands

- Enbanced Passive Mixer-First Receiver Driving an Impedance with 40dB/Decade Roll-Off, Achieving +12dBm Blocker-P1dB, +33dBm IIP3 and Sub-2dB NF Degradation for a OdBm Blocker Sashank Krishnamurthy, Ali M. Niknejad University of California, Berkeley, USA

- A Quadrature Class-G Complex-Domain Doherty Digital Power Amplifier Shih-Chang Hung, Si-Wook Yoo, Sang-Min Yoo Michigan State University, USA

- A Coupler-Based Differential Doberty Power Amplifier with Built-In Baluns for High mm-Wave Linear-Yet-Efficient Gbit/s Amplifications Huy Thong Nguyen, Hua Wang Georgia Tech, USA

- A 350mV Complementary 4–5GHz VCO Based on a 4-Port Transformer Resonator with 195.8dBc/Hz Peak FOM in 22nm FDSOI Omar El-Aassar, Gabriel M. Rebeiz University of California, San Diego, USA

- A 39GHz 64-Element Phased-Array CMOS Transceiver with Built-In Calibration for Large-Array 5G NR

Yun Wang<sup>1</sup>, Rui Wu<sup>1</sup>, Jian Pang<sup>1</sup>, Dongwon You<sup>1</sup>, Ashbir Aviat Fadila<sup>1</sup>, Rattanan Saengchan<sup>1</sup>, Xi Fu<sup>1</sup>, Daiki Matsumoto<sup>1</sup>, Takeshi Nakamura<sup>1</sup>, Ryo Kubozoe<sup>1</sup>, Masaru Kawabuchi<sup>1</sup>, Bangan Liu<sup>1</sup>, Haosheng Zhang<sup>1</sup>, Junjun Qiu<sup>1</sup>, Hanli Liu<sup>1</sup>, Wei Deng<sup>1</sup>, Naoki Oshima<sup>2</sup>, Keiichi Motoi<sup>2</sup>, Shinichi Hori<sup>2</sup>, Kazuaki Kunihiro<sup>2</sup>, Tomoya Kaneko<sup>2</sup>, Atsushi Shirane<sup>1</sup>, Kenichi Okada<sup>1</sup>

<sup>1</sup>Tokyo Institute of Technology, Japan, <sup>2</sup>NEC, Japan

- A 24.5–43.5GHz Compact RX with Calibration-Free 32–56dB Full-Frequency Instantaneously Wideband Image Rejection Supporting Multi-Gb/s 64-QAM/256-QAM for Multi-Band 5G Massive MIMO Min-Yu Huang<sup>1</sup>, Taiyun Chi<sup>2</sup>, Fei Wang<sup>1</sup>, Sensen Li<sup>1</sup>, Tzu-Yuan Huang<sup>1</sup>, Hua Wang<sup>1</sup> <sup>1</sup>Georgia Tech, USA, <sup>2</sup>Speedlink Technology, USA

- A 51.5–64.5GHz Active Phase Shifter Using Linear Phase Control Technique with 1.4° Phase Resolution in 65-nm CMOS Tianjun Wu, Chenxi Zhao, Huihua Liu, Yunqiu Wu, Yiming Yu, Kai Kang

UESTC, China

A 6.5-GHz Cryogenic All-Pass Filter Circulator in 40-nm CMOS for Quantum Computing Applications

Andrea Ruffino<sup>1</sup>, Yatao Peng<sup>1</sup>, Fabio Sebastiano<sup>2</sup>, Masoud Babaie<sup>2</sup>, Edoardo Charbon<sup>1</sup> <sup>1</sup>EPFL, Switzerland, <sup>2</sup>Technische Universiteit Delft, The Netherlands

<u>Student Paper Contest Eligibility</u>: The student must have been a full-time student (9 hours/term graduate, 12 hours/term undergraduate) during the time the work was performed. The student must also be the lead author of the paper and must present the paper at the Symposium.

#### Monday 3 June 2019 08:00–09:40 252AB Session RMo1A: RF Receiver Building Blocks Chair: Edmund Balboni, Analog Devices Co-Chair: Domine Leenaerts, NXP Semiconductors

#### RMo1A-1 08:00

#### A 1.2–2.8GHz Tunable Low-Noise Amplifier with 0.8–1.6dB Noise Figure

Hao Gao, Zhe Song, Zhe Chen, Domine M.W. Leenaerts, Peter G.M. Baltus; Technische Universiteit Eindhoven, The Netherlands

**Abstract:** This paper presents a tunable wideband low-noise amplifier (LNA) covering 1.2 to 2.8 GHz and is realized in a 0.25  $\mu$ m SiGe:C BiCMOS technology. The LNA covers 80% fractional bandwidth in 16 states using a dual-LC tanks input broadband noise matching technique and a switch capacitor output frequency selection network. The measured minimal noise figure (NF) is 0.8 dB at 1.4 and 1.8 GHz, and the average NF is 1.2 (±0.4) dB from 1.2 to 2.8 GHz. The best gain is 14 dB at 2 GHz and with ±0.5 dB flatness bandwidth covers from 1.4 GHz to 2.6 GHz. The measured input 1-dB compression point and input IP3 are better than -8 dBm and 3.5 dBm, respectively.

#### RMo1A-2 08:20

# A 28-GHz CMOS LNA with Stability-Enhanced $\mathrm{G}_{\mathrm{m}}\text{-}\mathrm{Boosting}$ Technique Using Transformers

Sunwoo Kong, Hui-Dong Lee, Seunghyun Jang, Jeehoon Park, Kwang-Seon Kim, Kwang-Chun Lee; ETRI, Korea

**Abstract:** In this paper, we propose a low noise amplifier (LNA) using a  $g_m$ -boosting technique with improved stability using transformers in the millimeter-wave (mm-Wave) band. The transformer composed of three inductors improves not only stability, but also gain and low-noise performance of the LNA. The conditions for stability shows that the proposed structure can guarantee good stability over a high frequency range. The chip was fabricated using the TSMC 65-nm CMOS process and it has an active chip area of  $0.11 \mu m^2$ . The fabricated LNA has a gain of 18.33 dB and a noise figure (NF) of 3.25-4.2 dB. The stability factor  $\mu$  values are 9.7 and 5.2 at the source and load sides of the LNA, respectively. The 3-dB bandwidth of the LNA is 24.9-32.5 GHz and the chip consumes 17.1-mA current from a 1.2-V supply.

## RMo1A-3 08:40

#### Ka-Band CMOS Absorptive SP4T Switch with One-Third Miniaturization

Bosung Suh, Byung-Wook Min; Yonsei University, Korea

**Abstract:** An Ka-band absorptive single-pole four-throw (SP4T) switch in 28-nm CMOS process is presented. By capacitive matching and loading method, only four  $\lambda/6$  transmission lines (t-line) are used for the proposed switch without additional series switches. The length of the t-line used in the proposed switch is only 1/3 of that of the quarter-wave t-line based absorptive switch. To improve switch performance, low threshold-voltage transistors and source and drain of transistors are biased for power handling capability. The measured insertion loss and isolation are 3.5 dB and 20 dB at 28 GHz. Return losses of on-state and off-state ports are less than -10 dB and -16 dB from 26 GHz to 33 GHz. The measured input 1-dB compression point is more than 15 dBm. The chip area is 0.53 mm<sup>2</sup> and electrical size is  $0.0047 \times (\lambda_g)^2$  excluding pads and internal matching circuits that is the smallest electrical size among the millimeter-wave CMOS absorptive SP4T switches.

#### RMo1A-4 09:00

# A Compact, High-Power, 60GHz SPDT Switch Using Shunt-Series SiGe PIN Diodes

Yunyi Gong, Jeffrey W. Teng, John D. Cressler; Georgia Tech, USA

**Abstract:** This work describes the design of a compact, 60 GHz, SPDT switch implemented using PIN diodes in a 130 nm SiGe BiCMOS technology. The SPDT RF switch employs a novel shunt-series topology with a resistive biasing scheme to "self-reverse-bias" the off-state shunt diode, thereby improving power handling capability of the SPDT. A coupled inductor matching network is used to minimize the switch size. The proposed design achieves a minimum insertion loss of 2.0 dB, more than 26 dB of isolation, and input-referred P1dB (at 60 GHz) of 22 dBm, with a 0.20  $\times$  0.33 mm<sup>2</sup> footprint.

#### Monday 3 June 2019 08:00-09:40 254AB

#### Session RMo1B: Advanced Devices, Characterization, and Modeling for Millimeter-Wave Applications Chair: Alvin Joseph, GLOBALFOUNDRIES

Co-Chair: Edward Preisler, TowerJazz

#### RMo1B-1 08:00

#### Low-Cost, High-Gain Antenna Module Integrating a CMOS Frequency Multiplier Driver for Communications at D-Band

Francesco Foglia Manzillo, José Luis Gonzalez-Jimenez, Antonio Clemente, Alexandre Siligaris, Benjamin Blampey, Cedric Dehos; CEA-Leti, France

**Abstract:** This paper presents a compact D-band antenna module for ultrafast short-range communications. The system comprises a planar lens fed by an antenna-in-package embedding an integrated 28-nm bulk CMOS frequency multiplier. Both lens and primary source are fabricated using low-cost printed circuit board (PCB) technology. The module achieves a peak gain of 25 dBi and works between 114 GHz and 138 GHz with a gain drop lower than 3 dB. The proposed solution paves the way for low-loss and low-profile wireless systems entirely integrated in planar multilayer substrate modules.

#### RMo1B-2 08:20

#### Scalable Analytical Model of 1.7THz Cut-Off Frequency Schottky Diodes Integrated in 55nm BiCMOS Technology

Vincent Gidel<sup>1</sup>, Frédéric Gianesello<sup>1</sup>, Pascal Chevalier<sup>1</sup>, Grégory Avenier<sup>1</sup>, Nicolas Guitard<sup>1</sup>, Victor Milon<sup>1</sup>, Michel Buczko<sup>1</sup>, Charles-Alex Legrand<sup>1</sup>, Cyril Luxey<sup>2</sup>, Guillaume Ducournau<sup>3</sup>; <sup>1</sup>STMicroelectronics, France, <sup>2</sup>Polytech'Lab (EA 7498), France, <sup>3</sup>IEMN (UMR 8520), France

**Abstract:** In this paper, an innovative Schottky diode architecture is proposed and implemented in 55 nm BiCMOS technology. A State-of-the-art 1.7 THz cut-off frequency is measured and an analytical scalable model is proposed and experimentally validated paving the way for further performance improvement. In addition, this analytical model can be integrated in a Design Kit library in order to enable sub-THz Schottky diode-based circuit designs in advanced BiCMOS.

## RMo1B-3 08:40

#### Excellent 22FDX Hot-Carrier Reliability for PA Applications

T. Chen<sup>1</sup>, Chi Zhang<sup>1</sup>, W. Arfaoui<sup>2</sup>, Abdellatif Bellaouar<sup>1</sup>, S. Embabi<sup>1</sup>, G. Bossu<sup>2</sup>, M. Siddabathula<sup>2</sup>, K.W.J. Chew<sup>3</sup>, S.N. Ong<sup>3</sup>, M. Mantravadi<sup>1</sup>, K. Barnett<sup>1</sup>, J. Bordelon<sup>1</sup>, R. Taylor<sup>1</sup>, S. Janardhanan<sup>1</sup>; <sup>1</sup>GLOBALFOUNDRIES, USA, <sup>2</sup>GLOBALFOUNDRIES, Germany, <sup>3</sup>GLOBALFOUNDRIES, Singapore

**Abstract:** This work shows the excellent HCI (hot-carrier injection) reliability that 22FDX demonstrates for mmWave PA applications. The underlying device physics to explain this performance are also shown. Due to the fact that fully depleted SOI (FDSOI) eliminates the lateral bipolar device, the MOSFETs in 22FDX technology have an increased BVDSs when compared to a device in a partially depleted SOI (PDSOI) technology. A 2-stack PA is presented that demonstrates excellent reliability against all HCI stress. The device aging model is built based on the device stress data specific for PA applications. RelXpert is used to simulate device aging based on the model and suggests excellent PA reliability even under the worst mismatch condition.

#### RMo1B-4 09:00

#### 22nm Fully-Depleted SOI High Frequency Noise Modeling up to 90GHz Enabling Ultra Low Noise Millimetre-Wave LNA Design

L.H.K. Chan<sup>1</sup>, S.N. Ong<sup>1</sup>, W.L. Oo<sup>1</sup>, K.W.J. Chew<sup>1</sup>, Chi Zhang<sup>2</sup>, Abdellatif Bellaouar<sup>2</sup>, W.H. Chow<sup>1</sup>, T. Chen<sup>2</sup>, R. Rassel<sup>2</sup>, J.S. Wong<sup>1</sup>, C.K. Lim<sup>1</sup>, C.W.F. Wan<sup>1</sup>, J. Kim<sup>1</sup>, W.H. Seet<sup>1</sup>, David L. Harame<sup>3</sup>; <sup>1</sup>GLOBALFOUNDRIES, Singapore, <sup>2</sup>GLOBALFOUNDRIES, USA, <sup>3</sup>Research Foundation CUNY, USA

**Abstract:** This paper reports the high frequency (HF) noise characterized performance and modeling on 22nm FD-SOI technology transistor (GLOBALFOUNDRIES' 22FDX technology) from 2 GHz to the maximum E-band millimetre-Wave (mmWave) frequency of 90 GHz. The measurement was performed using the Focus Microwaves noise system with different customised setups and optimised for each discrete frequency bands. The data measured from each frequency bands were subsequently combined to produce the noise spectrum covering from 2 GHz to 90 GHz, with high accuracy, good continuity and excellent correlation to the compact model. The 22FDX technology transistor demonstrated very low mmWave noise figure, which is favourable for RF and mmWave applications such as LNA.

#### RMo1B-5 09:20

#### 22nm Ultra-Thin Body and Buried Oxide FDSOI RF Noise Performance

Ousmane M. Kane<sup>1</sup>, Luca Lucci<sup>1</sup>, Pascal Scheiblin<sup>1</sup>, Sylvie Lepilliet<sup>2</sup>, François Danneville<sup>2</sup>, <sup>1</sup>CEA-Leti, France, <sup>2</sup>IEMN (UMR 8520), France

**Abstract:** The drastic downscaling of the transistor size along with advances in material sciences allowed the development of low power CMOS technologies with competitive RF figure of merits suitable for millimeter applications. In this context, this paper presents the RF and noise characterization (up to 110 GHz) of an advanced 22 nm UTBB FDSOI technology developed by Globalfoundries. In addition to the excellent DC performance, the technology presents promising RF characteristics. Indeed, a maximum transconductance of 1.78 S/mm and a F<sub>max</sub> of 435 GHz are achieved. The technology also offers a state-of-the-art minimum noise figure (NF<sub>min</sub>) of 0.45 dB at 20 GHz (with an associated Gain of 13 dB) for a drain current of 185 mA/mm.

#### Monday 3 June 2019 08:00-09:40 257AB

#### Session RMo1C: Millimeter-Wave Radar and Imaging Systems Chair: Shahriar Shahramian, Nokia Bell Labs Co-Chair: Jane Gu, University of California, Davis

#### **RMo1C-1** 08:00 A 76–81GHz FMCW Transceiver with 3-Transmit, 4-Receive Paths and 15dBm Output Power for Automotive Radars

Zongming Duan<sup>1</sup>, Dongfang Pan<sup>1</sup>, Bowen Wu<sup>2</sup>, Yan Wang<sup>2</sup>, Bingbing Liao<sup>2</sup>, Dong Huang<sup>3</sup>, Yanhui Wu<sup>4</sup>, Daiguo Xu<sup>4</sup>, Hua Xu<sup>4</sup>, Wei Lv<sup>2</sup>, Yuefei Dai<sup>2</sup>, Pei Li<sup>2</sup>, Yan Wang<sup>3</sup>, Fujiang Lin<sup>1</sup>, <sup>1</sup>USTC, China, <sup>2</sup>ECRIEE, China, <sup>3</sup>Tsinghua University, China, <sup>4</sup>CETC 24, China

**Abstract:** A fully-integrated 76–81GHz FMCW transceiver in 65-CMOS is presented for automotive radar applications. The transceiver consists of 3-transmitter, 4-receiver, FMCW synthesizer and ADC with decimation filters. The transmitter, with a TX chain including a push-push doubler, a 3-stage power amplifier employing neutralization technique and 2 power-combined topologies, shows an output power of 15dBm. The receiver, with an LNA employing a 3-stage neutralized common source (CS) with inductive degeneration, achieves a noise figure of 15dB, an input P-1dB of -20dBm, and an ENOB of 10.2-b for ADC. The double tuning modulated PLL provides FMCW waveform with -81dBc/Hz phase noise at 1MHz offset and chirp rate of 50MHz/µs. The power consumption of the entire transceiver is 1.06W.

# RMo1C-208:20Reconfigurable 60-GHz Radar Transmitter SoC with Broadband FrequencyTripler in 45nm SOI CMOS

Wooram Lee, Tolga Dinc, Alberto Valdes-Garcia; IBM T.J. Watson Research Center, USA

**Abstract:** A reconfigurable 60-GHz radar transmitter with a broadband frequency tripler is proposed to support CW/FMCW, pulse, and PMCW radar waveforms from a single front-end. The proposed IC consists of a wide-band frequency tripler, a two-stage driver, two power mixers with baseband circuitry and serial I/O circuitry. The IC measurements in CW mode operation show an output power of 12.8 dBm (average) and 14.7 dBm (peak) from 54 GHz to 67 GHz with harmonic suppression greater than 27 dB. Pulse and PMCW mode operations are also demonstrated to generate short pulses with the minimum pulse width of 25 ps corresponding to 40 GHz signal bandwidth and 10-Gb/s PRBS modulated signals, respectively. Fabricated in a 45-nm CMOS SOI process, the IC consumes 0.51 W and occupies an active area of 1.95 mm<sup>2</sup> excluding pads.

## RMo1C-3 08:40

#### A 94GHz 2×2 Phased-Array FMCW Imaging Radar Transceiver with 11dBm Output Power and 10.5dB NF in 65nm CMOS

Dong Huang<sup>1</sup>, Li Zhang<sup>1</sup>, Huabing Zhu<sup>2</sup>, Boshen Chen<sup>2</sup>, Yang Tang<sup>2</sup>, Yan Wang<sup>1</sup>; <sup>1</sup>Tsinghua University, China, <sup>2</sup>CAEP, China

**Abstract:** This paper presents a 94GHz 2×2 phased-array frequency-modulated continuous wave (FMCW) imaging radar transceiver. The transceiver consists of two receiving paths, two transmitting paths and a local oscillator (LO) generation path. In order to improve gain and noise performance, multi-paralleled transistors with small number-of-fingers are used to design power amplifier (PA) and low noise amplifier (LNA). A 24GHz voltage-controlled oscillator (VCO) is used to generate wideband FMCW signals, and two differential push-push cascode doublers are used to act as a quadrupler, which has a low power and high stability. Phase shifter (PS) with constant insertion loss (IL) compensation is used to achieve constant gain among different phase states. The LO path has a continuous frequency tuning range of 14GHz. The transmitter has a maximum output power of 11 dBm and 2.8dB power flatness over 14GHz bandwidth. The receiver has a conversion gain of 20dB and a noise figure (NF) of 10.5dB.

#### RMo1C-4 09:00

#### X/Ku-Band Four-Channel Transmit/Receive SiGe Phased-Array IC

Prabir Saha, Sriram Muralidharan, Jinzhou Cao, Ozan Gurbuz, Christopher Hay; Analog Devices, USA

**Abstract:** This paper presents a phased-array core chip integrating four transmit/receive channels and supporting circuitry on a single chip working over 8–16 GHz, covering X and Ku frequency bands. Each RX and TX channel has a VGA and a phase shifter featuring precise amplitude and phase control for RF beamforming. The phase-compensated VGA provides 16 dB of gain control range in 0.5 dB steps while limiting the corresponding phase variation to 3°. The phase shifter, based on the principles of a vector modulator, provides 360° phase control range with resolution better than 2.8°, rms phase and gain error less than 2.8° and 0.3 dB respectively. Each RX channel has more than 10 dB of gain, and the noise figure for maximum gain condition is better than 10 dB. In receive mode, input P1dB is -16 dBm per channel and in transmit mode, output P1dB is greater than 9 dBm over 8–16 GHz. Each RX and TX channel draws 65 mA and 85 mA respectively from a 3.3 V supply. The chip, fabricated in a 0.18 $\mu$ m SiGe BiCMOS technology, occupies 4mm × 4mm and was put in a 7mm × 7mm LGA package.

# RMo1C-509:20Ultra-Wideband8-45GHz Transmitter Front-End for a ReconfigurableFMCW MIMO Radar

Mantas Sakalas, Songhui Li, Niko Joram, Paulius Sakalas, Frank Ellinger; Technische Universität Dresden, Germany

**Abstract:** This paper presents an ultra-wideband 8–45 GHz FMCW MIMO radar transmitter (Tx) front-end, designed in a 130 nm SiGe BiCMOS technology. Various design techniques were applied to achieve the ultra-wide bandwidth, high linearity and the output power, which is at the edge for the given technology. The measured output power at 1 dB compression point was 15–20 dBm in a frequency range of 8–45 GHz and 3 dB output power flatness of 17–20 dBm was achieved for a 9–41 GHz bandwidth. The compact design features a total active IC area of 2.72 mm<sup>2</sup> and a peak overall system PAE of 9%. The total DC power consumption was 1.45 W.

#### Monday 3 June 2019 10:10–11:50 252AB Session RMo2A: 5G and Millimeter-Wave Beamforming Building Blocks Chair: Ruonan Han, MIT Co-Chair: Abdellatif Bellaouar, GLOBALFOUNDRIES

#### RMo2A-1 10:10

# A 51.5–64.5GHz Active Phase Shifter Using Linear Phase Control Technique with 1.4° Phase Resolution in 65-nm CMOS

Tianjun Wu, Chenxi Zhao, Huihua Liu, Yunqiu Wu, Yiming Yu, Kai Kang; UESTC, China

**Abstract:** This paper presents a V-band active phase shifter using proposed linear phase control technique with  $1.4^{\circ}$  phase step in 65-nm CMOS technology. Different from conventional active phase shifter, the linear phase control technique achieves a linear relationship between output phase and control signals. It makes the control of output phase more accurate and greatly improves the phase resolution. Furthermore, a current-reuse technique is used to improve gain in mm-wave frequency. The measurement results show that the measured 3-dB bandwidth of 51.5 - 64.5 GHz is achieved. The measured RMS phase error of 8-bit phase resolution is  $0.5^{\circ} - 1.2^{\circ}$  in 3-dB bandwidth and the measured RMS gain variation error is 0.17 - 0.25 dB. The measured input-referred P1dB at maximum gain phase states is -5 dBm. The chip consumes 16.9 mA from 1.2 V voltage supply and the core area of the phase shifter is 720 µm × 560 µm.

## **RMo2A-2 10:30** Digitally-Assisted 27–33GHz Reflection-Type Phase Shifter with Enhanced Accuracy and Low IL-Variation

Jingjing Xia, Mahitab Farouk, Slim Boumaiza; University of Waterloo, Canada

**Abstract:** This paper presents a new millimeter-wave  $360^{\circ}$  digitally-assisted reflection-type phase shifter (DA-RTPS). It is composed of a cascade of three compact, low-loss and fully-differential transformer-based hybrid couplers with two of their ports terminated by switch-controlled capacitor banks. Each stage is configured to produce a phase change of up to  $60^{\circ}$ . An additional phase inverting stage is used to attain  $360^{\circ}$  of phase shift. The proposed DA-RTPS arrangement enabled low insertion loss (IL) variation and enhanced phase accuracy compared to single-stage RTPS-based typologies. A proof-of-concept prototype, implemented using 45nm silicon-on-insulator CMOS technology, demonstrated a 1-dB RF bandwidth spanning from 27 to 33 GHz, a low root-mean-square phase error of  $0.3^{\circ}$ , and an IL of 6.8 dB±0.25dB, while covering  $360^{\circ}$  of phase shift at 5.6° resolution. Furthermore, it maintained a group delay below ±12ps and an input 1dB compression point >7.3 dBm at all phase-shift settings between 27 and 33 GHz.

#### RMo2A-3 10:50

#### A 21 to 30-GHz Merged Digital-Controlled High Resolution Phase Shifter-Programmable Gain Amplifier with Orthogonal Phase and Gain Control for 5-G Phase Array Application

Wei Zhu<sup>1</sup>, Wei Lv<sup>2</sup>, Bingbing Liao<sup>2</sup>, Yanping Zhu<sup>2</sup>, Yuefei Dai<sup>2</sup>, Pei Li<sup>2</sup>, Lei Zhang<sup>1</sup>, Yan Wang<sup>1</sup>; <sup>1</sup>Tsinghua University, China, <sup>2</sup>ECRIEE, China

**Abstract:** This paper presents a 21 to 30-GHz merged passive vector sum phase shifter (PS) and programmable gain amplifier (PGA) with sub-degree phase resolution for 5-G phased array application. In PS, a transformer-based full-differential high-order resonant coupler functions as a quadrature generator (QG) with a novel layout strategy to achieve broad bandwidth, low loss, and accurate quadrature phase within only one inductor-footprint. Compared to the conventional transformer-based fourth order resonant coupler, the proposed resonant coupler with higher order features much wider quadrature bandwidth. Two phase invariant 6-bit binary-weighted arrays of vector modulators scale the quadrature signals to achieve the desired high resolution vector phase interpolation. In PGA, a phase invariant and dB-linear gain is achieved by adopting a "fractional-bit-based" PGA design. The chip prototype is fabricated in a 65-nm CMOS process, this implementation achieves 43% fractional BW<sub>-3dB</sub> (20 to 31-GHz). The phase control operates with 0.8° steps while maintaining a minimum RMS phase error of 0.42°, demonstrating the best phase accuracy when compared to state-of-the-art mm-wave PSs.

#### RMo2A-4 11:10

# A 20–43GHz VGA with 21.5dB Gain Tuning Range and Low Phase Variation for 5G Communications in 65-nm CMOS

Tianjun Wu, Chenxi Zhao, Huihua Liu, Yunqiu Wu, Yiming Yu, Kai Kang; UESTC, China

**Abstract:** This paper presents a broadband variable gain amplifier (VGA) with low phase variation in 65 nm CMOS technology. The mechanism of phase variation in CMOS VGA is analyzed. According to the analysis, the feedforward paths formed by parasitic capacitive and inductive couplings are one of the main factors that result in phase variation in CMOS VGA. In order to achieve low phase variation, a parasitic capacitor elimination technique is proposed to remove the feedforward path formed by gate-drain parasitic capacitor. Besides, an isolation enhancement layout technique is proposed to minimize the inductive coupling and parasitic capacitors in the layout of the variable gain stage. As results, the measured phase variation is  $0.2^{\circ} - 2^{\circ}$  in 18 GHz – 37 GHz and  $0.2^{\circ} - 5.4^{\circ}$  in 18 GHz – 45 GHz when the gain variation range is 21.5 dB. The measured peak gain is 14.5 dB with 3-dB bandwidth of 20 GHz – 43 GHz. The gain ripple in 3-dB bandwidth is < 2.5 dB. The noise figure and input-referred P1dB are 5.5 dB and -16.5 dBm in the maximum gain state, respectively. The chip consumes 30.8 mW from 1.1 V voltage supply and the core area is 370  $\mu$ m × 930  $\mu$ m.

#### RMo2A-5 11:30

# A 26-GHz Vector Modulator in 130-nm SiGe BiCMOS Achieving Monotonic 10-b Phase Resolution without Calibration

Ilker Kalyoncu<sup>1</sup>, Abdurrahman Burak<sup>1</sup>, Mehmet Kaynak<sup>2</sup>, Yasar Gurbuz<sup>1</sup>; <sup>1</sup>Sabanci University, Turkey, <sup>2</sup>IHP, Germany

**Abstract:** This paper presents a high-resolution (10-b) vector-modulator (VM) phase shifter (PS) in 130-nm SiGe BiCMOS targeting 5G applications at 26 GHz. It employs a Gilbert-cell RF core, the tail current of which is controlled by an 8-b low-power current-steering DAC and 2-b I/Q sign switches. The DAC includes an on-chip PTAT current reference with process compensation capabilities. A 2-stage RC polyphase filter (PPF) is used to generate the quadrature signals. Without any calibration or correction of PS control signals, the measured results demonstrate completely monotonic 2<sup>10</sup> phase states, covering the full 0–360° range without any dead zones or overlapping phase states. The worst case (maximum) phase difference between any adjacent states is 0.65°. The VM exhibits an average insertion loss of 0.5 dB at 26 GHz with a 3-dB BW of 8 GHz, an rms amplitude error of 0.2 dB, IP<sub>1dB</sub> of 2 dBm, and 23 mW dc power dissipation. Potential applications are in RF beamforming and RF self-interference cancellation.

#### Monday 3 June 2019 10:10–11:50 254AB Session RMo2B:

#### Digitally Assisted Front-Ends for Emerging Wireless Applications Chair: Debopriyo Chowdhury, Broadcom Co-Chair: Oren Eliezer, PHAZR

#### RMo2B-1 10:10

# A 20–32GHz Digital Quadrature Transmitter with Notched-Matching and Mode-Switch Topology for 5G Wireless and Backhaul

Huizhen Jenny Qian, Yiyang Shu, Jie Zhou, Xun Luo; UESTC, China

**Abstract:** In this paper, a mm-wave wideband digital quadrature transmitter with improved efficiency for the 5G wireless and backhaul communication is presented. A novel synthesized notched-matching network is proposed to decrease the impedance mismatch from the interconnection of power digital-to-analog converter (power-DAC) cells operating at mm-wave bands. The performance is further optimized at the low- and high-bands by mode-switch of the quadrature signal generator, interstage matching of sign map, and power-DAC output-matching, simultaneously. Based on the mechanisms mentioned above, a  $2 \times 10$ -bit digital quadrature transmitter operating at 20-32GHz is implemented and fabricated using a conventional 28-nm CMOS technology, which exhibits the saturated output power of 19.02dBm, 34.4% maximum drain efficiency, and maximum system efficiency of 22.1%, respectively. Such mm-wave transmitter can support 64QAM modulation signals with 3Gb/s data-rate, -28.9dB EVM, 9.96dBm output power, and -33.6dBc ACPR.

#### RMo2B-2 10:30

#### A Wideband Digital Polar Transmitter with Integrated Capacitor-DAC-Based Constant-Envelope Digital-to-Phase Converter

Tong Li, Liang Xiong, Yun Yin, Yangzi Liu, Hao Min, Na Yan, Hongtao Xu; Fudan University, China **Abstract:** This paper presents a wideband digital polar transmitter (DPTX) with integrated capacitor-DAC-based constant-envelope digital-to-phase converter (DPC). The switched-capacitor DAC topology is adopted to improve the linearity. The harmonic rejection and cell-reused techniques are employed to reject the  $3^{nd}/5^{th}$ -order harmonics and reduce the power consumption, respectively. The measurement results of DPC demonstrate the maximum INL and DNL of 1 and 0.8 degrees with the power consumption of 12.7mW@1.5GHz. The DPTX obtains the peak output power of 20.1dBm with 23.7% system efficiency and wideband frequency coverage over 1.2-2.5GHz with only 0.7dB power variation. When amplifying a 10MHz 64QAM LTE signal at 1.5GHz, it achieves -28.6dB EVM and 15.2% system efficiency at 15.0dBm average output power.

## RMo2B-3 10:50

# A 5GHz to 6GHz CMOS Transmitter for Full-Duplex Wireless with Wideband Digital Cancellation

Nimrod Ginzberg<sup>1</sup>, Dror Regev<sup>2</sup>, Genadiy Tsodik<sup>2</sup>, Shimi Shilo<sup>2</sup>, Doron Ezri<sup>2</sup>, Emanuel Cohen<sup>1</sup>; <sup>1</sup>Technion, Israel, <sup>2</sup>Toga Networks, Israel

**Abstract:** This paper presents a quadrature balanced transmitter, assisted by a digital equalization and predistortion self-interference cancellation technique for Full-Duplex wireless applications. An analysis of design trade-offs between low receiver (Rx) loss and high transmitter (Tx) efficiency is laid out and demonstrated on a 5GHz to 6GHz class AB power amplifier implemented in 180nm CMOS. Wideband cancellation of >48dB and >57dB at 20dBm and 10dBm Tx output power, respectively, is measured in CW. Cancellation of >30dB for an actual 160MHz 802.11ac OFDM packet around a carrier frequency of 5.2GHz together with EVM of -33dB is demonstrated. Measured Tx power added efficiency (PAE) for concurrent Tx-SIC operation is 35% and 6.4% at peak and RMS (10dB backoff) power, respectively. Rx loss is lower than 1.6dB at RMS Tx power within the signal frequency band.

### RMo2B-4 11:10

#### A Sub-mW All-Passive RF Front End with Implicit Capacitive Stacking Achieving 13dB Gain, 5dB NF and +25dBm OOB-IIP3

Vijaya Kumar Purushothaman, Eric Klumperink, Berta Trullas Clavera, Bram Nauta; University of Twente, The Netherlands

**Abstract:** This paper presents a sub-mW mixer-first RF front-end that exploits a novel capacitive stacking technique in an altered bottom-plate N-path filter/mixer to achieve passive voltage gain and high-linearity at low noise figure. Capacitive stacking is realized implicitly by reading out the voltage from the bottom-plate of N-path capacitors instead of their top-plate, which provides a 2× gain at the read-out capacitors. Additional passive voltage gain is achieved using impedance upconversion while improving the out-of-band linearity performance of small switches. With no other active circuitry, only clock generation circuits determine the total power consumption of this RF front-end. A prototype is fabricated in GF22nm FDSOI technology. Operating at  $f_{LO}$  = 1 GHz, the prototype achieves a voltage gain of 13 dB, 5 dB Noise Figure and +25/+66dBm Out-of-band IIP3/ IIP2 at 160MHz offset while consuming only 600 µW of power from a 0.8V supply.

#### RMo2B-5 11:30

#### A 0.3-to-1.3GHz Multi-Branch Receiver with Modulated Mixer Clocks for Concurrent Dual-Carrier Reception and Rapid Compressive-Sampling Spectrum Scanning

Guoxiang Han, Tanbir Haque, Matthew Bajor, John Wright, Peter R. Kinget; Columbia University, USA

**Abstract:** A flexible RF receiver is introduced that uniquely uses CW-modulated clocks for the downconversion mixers in its mixer-first and low-noise transconductance branches, thereby enabling tuned matching and reception concurrently at two RF carriers. Turning off the modulation reverts the receiver back to single-carrier operation, whereas using PN sequences to modulate the mixer clocks enables rapid, wideband compressive-sampling spectrum scanning. All three functions are accomplished within a single unified architecture. A prototype of the multi-branch modulatedmixer-clock receiver was developed in 65nm CMOS and operates from 0.3 to 1.3GHz. For singlecarrier reception, the receiver delivers 15MHz RF bandwidth, 42dB conversion gain, 3.3dB NF, +3.3dBm B1dB, and +12.2dBm OB-IIP3. Concurrent dual-carrier reception at 500MHz and 900MHz offers -8.4dBm B1dB and <6dB NF. In rapid CS spectrum scanning mode, the receiver achieves 66dB dynamic range with -75dBm sensitivity over a 630MHz RF span within 0.71µs and consumes 18.5nJ per detected signal.

#### Monday 3 June 2019 10:10-11:50 257AB

#### Session RMo2C: RF-Inspired Emerging Technologies and Applications Chair: Fabio Sebastiano, Technische Universiteit Delft Co-Chair: Renyuan (Ryan) Wang, BAE Systems

#### RMo2C-1 10:10

# A 0.5–20GHz RF Silicon Photonic Receiver with 120 dB•Hz<sup>2/3</sup> SFDR Using Broadband Distributed IM3 Injection Linearization

Navid Hosseinzadeh, Aditya Jain, Kang Ning, Roger Helkey, James F. Buckwalter; University of California, Santa Barbara, USA

**Abstract:** Radio-over-fiber (RoF) supports microwave and millimeter-wave communication with remote antenna heads. However, RoF links suffer from low spur-free dynamic range (SFDR) due to the low gain and high nonlinearity of silicon photonic (SiP) Mach-Zehnder modulators (MZM). This work demonstrates the first distributed silicon-germanium (SiGe) HBT LNA co-designed for linearization of a broadband SiP-based RoF link. The SiGe LNA features a distributed LNA intermodulation (IM) injection scheme that is inherently wideband, improving IIP3 over a 10 GHz range. The assembled SiGe LNA and SiP MZM prototype demonstrates an SFDR as high as 120dB  $\cdot$ Hz<sup>2/3</sup> at 9 GHz, a 19 dB improvement over previous SiP RoF links.

#### RMo2C-2 10:30

# A 65nm CMOS Continuous-Time Electro-Optic PLL (CT-EOPLL) with Image and Harmonic Spur Suppression for LIDAR

Ali Binaie, Sohail Ahasan, Harish Krishnaswamy; Columbia University, USA

**Abstract:** An integrated continuous-time electro-optic phase-locked loop (CT-EOPLL) is presented that features image and harmonic spur suppression, and is used in a frequency-modulated continuous-wave (FMCW) LIDAR. The proposed EOPLL has its loop bandwidth equal to its reference frequency, which enables it to relax the trade-off between chirp bandwidth and Mach-Zehnder (MZ) delay and consequently reduce the area and loss associated with the silicon-photonic delay implementation by 10×. Image and harmonic spurs are rejected through single-sideband (SSB) and harmonic-reject (HR) mixing techniques. This EO-PLL is integrated in 65nm CMOS technology, suppresses the highest spur by more than 25dB, and is used in a LIDAR system that can detect an object at ranges exceeding 3.3 meters with an RMS depth precision of 558 $\mu$ m at 2m distance and 9.4mm depth resolution.

#### RMo2C-3 10:50

# A 6.5-GHz Cryogenic All-Pass Filter Circulator in 40-nm CMOS for Quantum Computing Applications

Andrea Ruffino<sup>1</sup>, Yatao Peng<sup>1</sup>, Fabio Sebastiano<sup>2</sup>, Masoud Babaie<sup>2</sup>, Edoardo Charbon<sup>1</sup>; <sup>1</sup>EPFL, Switzerland, <sup>2</sup>Technische Universiteit Delft, The Netherlands

**Abstract:** Cryogenic solid-state quantum processors require classical control and readout electronics; to achieve compactness and scalability, cryogenic integrated circuits have been recently proposed for this goal. Circulators are widely used in readout circuits, however they are typically discrete bulky devices, thus preventing miniaturization. To address this issue, we propose a fully integrated 40-nm CMOS 6.5-GHz circulator operating from 300K to 4.2 K. At 300 K, it achieves a 2.2-dB insertion loss, an 18-dB isolation, and a 2.4-dB noise figure over the 1-dB bandwidth from 5.6GHz to 7.4 GHz, with a core power of only 2.5mW. This improves to 2.1mW core power at 4.2 K, while showing 1.3-dB insertion loss and 17-dB isolation over the 1-dB bandwidth from 5.8 GHz to 7.6 GHz. The circuit achieves a record-low core power and a  $1.6 \times$  wider fractional bandwidth than the state-of-the-art, thus allowing its use for multiple channels in power-constrained cryogenic refrigerators. These advances are enabled by a fully-passive architecture based on LC all-pass filters, allowing the use of a lower clock frequency than in prior art.

#### RMo2C-4 11:10

#### Design Considerations for Spin Readout Amplifiers in Monolithically Integrated Semiconductor Quantum Processors

M.J. Gong<sup>1</sup>, U. Alakusu<sup>1</sup>, S. Bonen<sup>1</sup>, M.S. Dadash<sup>1</sup>, Luca Lucci<sup>2</sup>, H. Jia<sup>3</sup>, L.E. Gutierrez<sup>3</sup>, W.T. Chen<sup>3</sup>, D.R. Daughton<sup>4</sup>, G.C. Adam<sup>5</sup>, S. Iordănescu<sup>5</sup>, M. Păşteanu<sup>5</sup>, N. Messaoudi<sup>6</sup>, David L. Harame<sup>2</sup>, A. Müller<sup>5</sup>, R.R. Mansour<sup>3</sup>, S.P. Voinigescu<sup>1</sup>; <sup>1</sup>University of Toronto, Canada, <sup>2</sup>GLOBALFOUNDRIES, Germany, <sup>3</sup>University of Waterloo, Canada, <sup>4</sup>Lake Shore Cryotronics, USA, <sup>5</sup>IMT Bucharest, Romania, <sup>6</sup>Keysight Technologies, Canada

**Abstract:** The high frequency performance of all active and passive devices in a production 22nm FDSOI CMOS technology was measured up to 40 GHz over temperature down to 3.3 Kelvin, targeting applications in cryogenic and quantum computing ICs. It was found that the quality factor of the passives and the  $f_T$  and  $f_{MAX}$  of both p- and n-MOSFETs improved at 3.3 K. More importantly for circuit design, the peak- $f_T$  and peak- $f_{MAX}$  current densities, and the MOM capacitor and polysilicon resistor values show no variance with temperature. This information and the measured I-V characteristics of electron and hole single- and double-quantum dot structures, measured at 2 K and representative of qubits, were used to design monolithically integrated double quantum dots with readout transimpedance amplifiers output matched to 50  $\Omega$ . Transimpedance gain, S<sub>21</sub>, and bandwidth of 108 dB $\Omega$ , 19 dB, and 7.5 GHz, respectively, were measured at 300 K with only 4.5 mW power consumption and S<sub>22</sub> < -10 dB up to 60 GHz.

#### RMo2C-5 11:30

#### Direct Digital Synthesizer with 14GS/s Sampling Rate Heterogeneously Integrated in InP HBT and GaN HEMT on CMOS

Steven Eugene Turner, Mark E. Stuenkel, Gary M. Madison, Justin A. Cartwright, Richard L. Harwood, Joseph D. Cali, Steve A. Chadwick, Michael Oh, John T. Matta, James M. Meredith, Justin M. Byrd, Lawrence J. Kushner; BAE Systems, USA

**Abstract:** A 14 GS/s direct digital synthesizer (DDS) heterogeneously integrated with InP and GaN on CMOS is presented. The DDS includes over 6 million 45 nm CMOS FETs, 2151 InP HBTs, 2 GaN HEMTs, and 9930 heterogeneous interconnects, making it the most complex heterogeneously integrated mixed-signal circuit reported to date. By heterogeneously integrating multiple technologies, a high output power of 6.9 dBm is achieved while maintaining better than 37 dBc Nyquist SFDR and 8.7 W power consumption — performance currently unachievable with state-of-the-art single-technology approaches.

#### Monday 3 June 2019 13:30–15:10 252AB

#### Session RMo3A: Millimeter-Wave Integrated Subsystems Chair: Pierre Busson, STMicroelectronics Co-Chair: Mona Hella, Rensselaer Polytechnic Institute

## **RMo3A-1 13:30** A 1V 54–64GHz 4-Channel Phased-Array Receiver in 45nm RFSOI with 3.6/5.1dB NF and -23dBm IP1dB at 28/37mW Per-Channel

Hyunchul Chung, Qian Ma, Gabriel M. Rebeiz; University of California, San Diego, USA