2014 IEEE Radio Frequency Integrated Circuits Symposium

> Tampa Bay, Florida, USA 1–3 June 2014

# PROGRAM

# Tampa Convention Center and Marriott Waterside Hotel and Marina

Sponsored by

IEEE Microwave Theory and Techniques Society IEEE Electron Devices Society and IEEE Solid-State Circuits Society

#### **RFIC Plenary Round-Table, Industry Showcase, and Reception**

#### Sunday Evening, 1 June 2014 Marriott Waterside Hotel and Marina

After a busy day immersed in RFIC Workshops, enjoy a relaxing evening with your RFIC colleagues at these special Sunday night RFIC events, to be held in the Tampa Marriott Waterside Hotel and Marina, just across the street from the Tampa Convention Center (TCC).

**17:30–19:00 Grand Ballroom** — **The Plenary Session** kicks off the evening with the Student Paper Awards ceremony followed by two outstanding plenary speakers, Dr. Pieter Hooijmans, VP R&D and Strategy at NXP, and Prof. Lawrence Larson, Dean of School of Engineering, Brown University. Please see pages 7–11 for more details.

**19:00–20:00 Grand Ballroom Foyer** — "Hot Chips and Cold Drinks" Industry Showcase, and Reception Part 1: Immediately following the Plenary Session is the RFIC Reception held in the foyer just outside the ballroom (with a spectacular view of the marina). Cold drinks and appetizers will be provided while you connect with old friends, make new acquaintances, and catch up on the latest news in the wireless industry.

This year for the first time, the most innovative and highly-rated industrial papers will be highlighted in the Industry Showcase, held concurrently with the reception. Authors of these papers will be present for discussion of their work, summarized in poster format. Media will be present to cover this event, making it an excellent opportunity to announce the latest RFIC developments and breakthroughs. Please see pages 12–13 for more details.

**20:00–21:00 Grand Ballroom** — **The Inaugural RFIC Plenary Round Table** will feature luminaries from the RFIC community engaging in a lively discussion, in a casual, talk-show format, led by Prof. Hossein Hashemi, USC. Panelists include our two plenary speakers (listed above), along with Kamal Sahota, VP Qualcomm, Reza Rofougaran, SVP Broadcom, Zdravko Boos, Intel Fellow, and Peter Gammel, CTO Skyworks. Please see page 14 for more details.

#### 21:00-22:00 Grand Ballroom Foyer - Reception Part 2

Admittance to all RFIC Sunday evening events is included with the RFIC Symposium registration and Superpass registration. Additionally, Sunday-night-only tickets can be purchased for those who cannot attend the rest of the RFIC Symposium but do not want to miss these great events. Please see <u>http://rfic-ieee.org/</u> for more details.

The RFIC Receptions are sponsored by the RFIC Steering Committee, and through the generous support of our cooperate sponsors:

|                                |                                                     |                 | , n -                                                       |                                                          |                            |

|--------------------------------|-----------------------------------------------------|-----------------|-------------------------------------------------------------|----------------------------------------------------------|----------------------------|

| Event                          | Location                                            | Saturday 31 May | Sunday 1 June                                               | Sunday 1 June Monday 2 June                              | Tuesday 3 June             |

| Registration                   | TCC 2 <sup>nd</sup> Lobby                           | 08:00-18:00     | 07:00-                                                      | 07:00–19:00                                              | 07:00-18:00                |

| Speakers' Breakfast            | TCC Ballroom A                                      |                 |                                                             | 07:00-08:00                                              |                            |

| Workshop Breakfast             | TCC Ballroom D                                      |                 | 07:00-                                                      | 07:00-08:00                                              |                            |

| Workshops & Short Courses      | TCC 10-25                                           |                 | 08:00-                                                      | 08:00-17:00                                              |                            |

| Workshop Lunch                 | TCC Ballroom D                                      |                 | 12:00-                                                      | 12:00-13:00                                              |                            |

| Panel Sessions                 | TCC Ballroom A (Monday)<br>TCC Ballroom B (Tuesday) |                 |                                                             | 12:00–13:30                                              | -13:30                     |

| Steering Comm. Lunch Meeting   | Marriott Florida Salon 4/5                          |                 |                                                             | 13:00-14:30                                              |                            |

| TPC Lunch Meeting              | Marriott Florida Salon 4/5                          |                 |                                                             |                                                          | 13:00-14:30                |

| Technical Sessions             | TCC 10/11, 13/14, 15/16, 18                         |                 |                                                             | 08:00-09:40<br>10:10-11:50<br>13:30-15:10<br>15:40-17:20 | 08:00-09:40<br>10:10-11:50 |

| Interactive Forum              | TCC Ballroom C/D                                    |                 |                                                             |                                                          | 13:30-16:00                |

| Plenary Session                | Marriott Grand Ballroom                             |                 | 17:30–19:00                                                 |                                                          |                            |

| Industry Showcase & Receptions | Marriott Grand Ballroom<br>Foyer                    |                 | $\begin{array}{c} 19:00{-}20:00\\ 21:00{-}22:00\end{array}$ |                                                          |                            |

| Plenary Round Table            | Marriott Grand Ballroom                             |                 | 20:00-21:00                                                 |                                                          |                            |

# **RFIC Symposium Schedule (31 May – 3 June 2014)**

photos courtesy of Visit Tampa Bay and Robert La Follette

# **TABLE OF CONTENTS**

The RFIC Symposium is the premier IC conference focused exclusively on the latest developments in RF, Microwave, and mm-Wave Integrated Circuit technology and innovation from both industry and academia.

|        | Table of Contents                                                                                  |         |        |

|--------|----------------------------------------------------------------------------------------------------|---------|--------|

|        | Welcome Message from Chairs                                                                        |         |        |

|        | Steering Committee                                                                                 |         |        |

|        | Executive Committee                                                                                |         |        |

|        | Advisory Board<br>Technical Program Committee                                                      |         |        |

|        | RFIC 2014 Schedule                                                                                 |         |        |

|        | Plenary, Round-Table, Industry Showcase, and Reception Schedule                                    |         |        |

|        | Student Paper Award Finalists                                                                      |         |        |

|        | Plenary Speakers                                                                                   |         |        |

|        | Industry Showcase                                                                                  |         |        |

|        | Round Table Discussion                                                                             |         |        |

|        |                                                                                                    |         | -      |

|        | RM01R: Ellegy-Enlicent whereas markervers                                                          | 1       | כ<br>7 |

|        | RM02A: Mixed Signal Circuits at Gigahertz Frequencies                                              | 1       | /<br>0 |

|        | ≅ RM02B: K-Band Front-End ICs                                                                      |         |        |

|        | RM02B. A-band Fiont-End ICS<br>RM02C: Advanced PLL Techniques                                      | 2       | 1      |

|        | RM02D: Advancements in Distributive, Thermal, and Non-Linear Device Modeling                       | 2       | 5      |

| ¥۷     | RM02D: Advances in Wireless Mobile ICs                                                             |         |        |

| $\leq$ |                                                                                                    |         |        |

| ž      | RMO3B: mm-Wave PAs: 60GHz and Beyond<br>RMO3C: mm-Wave & Terahertz Frequency Generation Techniques | 2       | 9      |

|        | RM03D: Advances in Nano-Scale Devices and Novel Measurement Techniques for RFIC Designs            | 2       | 1      |

|        | RM04A: Wireless Connectivity Transceivers and Multi-Standard Digital Transmitters                  |         |        |

|        | RM04A. whereas connectivity transceivers and Multi-standard Digital transmitters                   |         |        |

|        | RM04B: Highly-Emicient Power Ampiners                                                              | )<br>20 | /<br>0 |

|        | RM04D: High-Speed Data Transceivers                                                                | 4       | 2      |

| _      |                                                                                                    |         |        |

|        | TU1C: mm-Wave Integration Technologies                                                             | 4       | 3      |

| 2      | DTI 124. Software Defined and Cognitive Dadie Techniques                                           | 4       | 5      |

| TUESD/ | RTU2A: Software-Defined and Cognitive Radio Techniques<br>RTU2B: Multiband PAs and Power Mixers    | 4       | )<br>7 |

|        | RTU2C: Sub-mm-Wave Transceivers                                                                    | 4       | /<br>0 |

| •      |                                                                                                    |         |        |

|        | ₹ RTUIF: Interactive Forum                                                                         | 5       | 1      |

|        | Panel Sessions                                                                                     | . 5     | 8      |

|        | Workshops and Short Courses                                                                        | . 6     | 0      |

|        | Registration                                                                                       | . 7     | 9      |

|        | Registration Rates                                                                                 | . 8     | 3      |

|        | Visa Information                                                                                   |         |        |

|        | Social Events/Guest Program                                                                        |         |        |

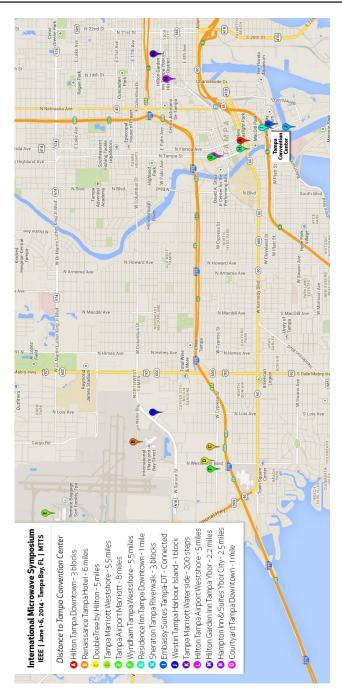

|        | Downtown Tampa Map                                                                                 |         |        |

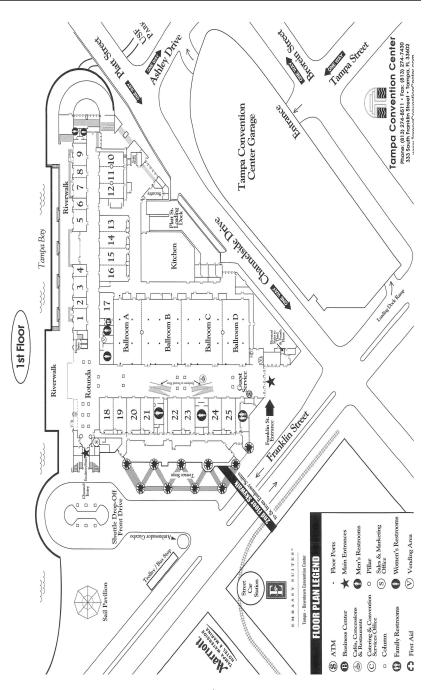

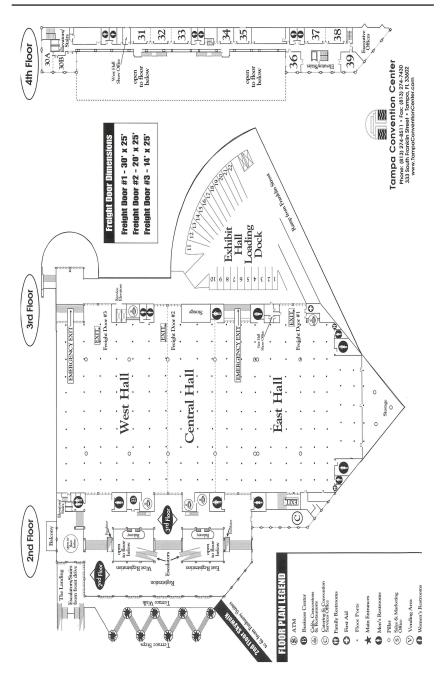

|        | Convention Center Maps                                                                             | . 9     | 4      |

#### Welcome Message from Chairs

We invite you to participate in the 2014 IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, to be held in Tampa, Florida on 1–3 June 2014. RFIC is the premier IC conference focused exclusively on the latest developments in RF, Microwave, and Millimeter Wave Integrated Circuit technology and innovation.

RFIC, the International Microwave Symposium (IMS), ARFTG, and the IMS Industry Exhibition make up "Microwave Week", the largest worldwide RF/microwave meeting of the year. Come to Microwave week to learn from the world's experts through a wide variety of technical sessions, interactive forums, panel sessions, workshops, short courses, industrial exhibits, application seminars, and historical exhibits. Share your knowledge with others by presenting your latest results. Expand your network. Catch up with old friends and colleagues. Return invigorated with new ideas and enthusiasm.

For the first time in 2014, RFIC will offer a number of new initiatives specifically geared towards the RFIC industry. First, a new 2-page industry brief format is introduced that allows the latest state-of-the-art RF IC design results to be presented, without requiring die photos and detailed schematics (as required in full-length, 4-page, submissions). Nevertheless, these 2-page briefs are subjected to the same technical criteria and rigorous review as full length papers. Secondly, the most innovative and highly-rated industrial papers, both 2- and 4-page, will be invited to present a poster (and optional demo) at a special Industry Showcase Session to held during the popular evening RFIC Reception on Sunday, 1 June 2014. In addition to all of the RFIC attendees, the media will be invited to cover this event, making it an excellent opportunity to announce the latest RFIC developments and breakthroughs.

Another new initiative in 2014 is geared towards enhancing academic submissions through programs supporting students. All of the RFIC student paper finalists will now receive complementary RFIC registration. In addition, the lead authors of the top 3 student papers will receive \$500 honorariums along special recognition at the RFIC Plenary Session where these awards will be announced.

Students have even more ways to participate (and receive financial assistance) this year. Students may volunteer to help with RFIC (and/or IMS) conference logistics in exchange for complementary conference registration, meals, T-shirts, and other benefits. For the first time in 2014, first and second-year RFIC PhD students may also participate in the PhD Student Sponsorship Initiative Program, joint with IMS. This program, established and sponsored by the MTT-S Administrative Committee, aims to engage these PhD students in the conference by having them complete technical assignments during the conference and report on them later in the week. Sponsorship includes complementary conference registrations (RFIC and IMS), lodging, and meals.

The 2014 RFIC Symposium will open on Sunday, 1 June 2014 with a lineup of eight full-day and five half-day workshops, four of which will be co-sponsored by IMS. Three additional joint RFIC/IMS workshops will be held on Monday. RFIC workshops cover a wide array of topics with presentations from experts in their respective fields, and historically have been highly attended and well received. This year's workshops cover some of the hottest topics in RFIC design. There are a number of workshops focused on power amplifier (PA) design including: silicon and GaN PAs for RF and mm-wave applications, highly-efficient power amplifiers and smart transmitters, power amplifiers for software defined radios, and critical supporting circuit designs such as GaN-based power supply modulators. In the frequency synthesis area, the "Frequency synthesis for 60-GHz and beyond: architectures and building blocks" workshops focused on some of the emerging technologies in RF transceivers include techniques for handling interference and self-interference, RF and wideband data-converters for transmitters and receivers, and EMC/EMI-aware design practices for reducing coupling and interference in integrated circuits.

The RFIC Plenary Session will be held on Sunday evening, in the Marriott Hotel directly across from the Convention Center. The plenary will begin with some overall conference highlights, followed by

the student paper awards. The plenary continues with two outstanding keynote addresses, given by two renowned industry leaders in the RF/Microwave Community. The first speaker is Pieter Hooijman, Vice President R&D and Strategy at NXP Semiconductors, whose talk is entitled "*How to differentiate with RF Silicon Technologies in high volume applications?*" The second speaker is Prof. Lawrence Larson, Dean of the School of Engineering at Brown University, who will present a talk entitled "*The Next Era of Wireless Communications — Enabling Revolutions in Health Care, Transportation, Energy, and the Environment.*" Be sure not to miss these engaging presentations.

Immediately following the Plenary Session is the new Industry Showcase Session concurrent with the RFIC Reception, providing a mix of "hot chips" and cold drinks. These events will be held in the foyer just outside of the Plenary Session, with a wonderful view of the water and marina. You'll want to be here.

The inaugural RFIC Plenary Round Table Discussion will be held next, with the stage set "talk show style". Leaders from the RFIC community will engage in a lively discussion on "*Beyond 4G Wireless Communications: An RFIC Perspective.*" Audience participation will also be welcome. Once the Round Table adjourns, the Reception will continue where it left off, with plenty of cold beverages to keep everyone cool.

Technical papers will be presented during RFIC oral sessions throughout Monday and on Tuesday morning, followed by the RFIC Interactive Forum on Tuesday afternoon. The Interactive Forum features papers presented in poster format, giving the attendees a chance to speak directly with the authors regarding their work.

During lunchtime on both Monday and Tuesday, the conference features panel sessions that are sure to draw lively debate among the panelists and audience. Monday's RFIC panel session is titled "*Fabless design: got any problem with that?*" and will debate the pros and cons of the fabless design model. The Tuesday panel session, held jointly with IMS, is titled "*Is Spectrum Explosion Muffled without Tunable RF?*" This panel brings together experts from across the wireless ecosystem to discuss the end user benefits, market opportunities, technical challenges and projected solutions surrounding the spectrum explosion and its impact on RF hardware, and whether or not tunable RF front-ends will step in to save the day.

Tampa offers a unique and exciting experience for everyone. A visit to the ever-growing downtown area, or the exciting Channelside and Ybor entertainment districts, will provide you with plenty to see. Tampa has a diverse selection of great restaurants and some of Florida's best attractions, including the Florida Aquarium, Busch Gardens Tampa Bay, the Straz Center for the Performing Arts, and Lowry Park Zoo. Of particular note are the new Tampa Bay History Center and the recently opened Tampa Museum of Art.

On behalf of the entire RFIC Steering Committee, we would like to extend to all of you a warm welcome to attend the 2014 RFIC Symposium. We are looking forward to an exciting program and hope you can join us in Tampa! For more details, please visit our website <a href="http://rfic-ieee.org">http://rfic-ieee.org</a>.

Lawrence Kushner General Chair BAE Systems

**Bertan Bakkaloglu** TPC Co-Chairman Arizona State University

Albert Wang TPC Co-Chairman UC Riverside

#### **Steering Committee**

Lawrence Kushner, BAE Systems, General Chair Bertan Bakkaloglu, Arizona State University, TPC Co-Chair Albert Wang, University of California at Riverside, TPC Co-Chair Kevin Kobayashi, RFMD, Finance Chair Robert Alongi, IEEE, Finances Walid Y. Ali-Ahmad, MediaTek, Workshop Chair Li Lin, Marvell Technology Group, Workshop Co-Chair Timothy M. Hancock, MIT Lincoln Laboratory, Panel Sessions Chair Stefano Pellerano, Intel, Digest & Publications Chair Domine Leenaerts, NXP Semiconductors, RFIC Program Book Freek van Straten, NXP Semiconductors, IMS Program Book Srenik Mehta, Qualcomm, Session Organization Waleed Khalil, Ohio State University, Transactions Special Issues Andre Hanke, Intel, Student Paper Contest Brian Floyd, North Carolina State University, Publicity Chair Amanda Scacchitti, Publicity & Advisor Bob Stengel, SiriusXM, Secretary Georg Boeck, Berlin Institute of Technology, European Liaison Patrick Yue, HKUST, Asia Pacific Liaison Fujiang Lin, USTC, Asia Pacific Liaison Michael Oakley, Georgia Institute of Technology, Webmaster Steven Turner, BAE Systems, Paper Submission Website Tim Lee, Boeing, Web Presence Elsie Cabrera, IEEE, Conference Manager Zaher Bardai, IMN Epiphany, VISAs

#### **Executive Committee**

Yann Deval, University of Bordeaux David Ngo, RFMD Jacques C. Rudell, University of Washington Lawrence Kushner, BAE Systems

#### **Advisory Board**

Natalino Camilleri, *RFWDS* Joseph Staudinger, *Freescale Semiconductor* Stefan Heinen, *RWTH Aachen University* Luciano Boglione, *Naval Research Laboratory* Jenshan Lin, *University of Florida*

#### **Technical Program Committee**

Ali Afsahi, Broadcom Walid Ali-Ahmad. MediaTek Himanshu Arora. Texas Instruments Edmund Balboni, Analog Devices Jean-Baptiste Begueret, University of Bordeaux Didier Belot, STMicroelectronics Georg Boeck, Technical University of Berlin Luciano Boglione, Naval Research Laboratory Pierre Busson. STMicroelectronics Natalino Camilleri. Nitero Sudipto Chakraborty, Texas Instruments Richard Chan, BAE Systems Glenn Chang, MaxLinear Jinghong Chen, Southern Methodist University Nick Cheng, Skyworks Solutions Yuhua Cheng, Peking University Yann Deval, University of Bordeaux Oren Eliezer, Xtendwave Kamran Entesari. Texas A&M University Ayman Fayed, Iowa State University Brian Floyd, North Carolina State University Eric Fogleman, MaxLinear Ranjit Gharpurey, University of Texas at Austin Danielle Griffith. Texas Instruments Jane Gu, University of California at Davis Aditya Gupta, Northrop Grumman Timothy M. Hancock, MIT Lincoln Laboratory Andre Hanke, Intel Ramesh Harjani, University of Minnesota Hossein Hashemi, University of Southern California Gary Hau, Anadigics Stefan Heinen, RWTH Aachen University Mona Hella, Rensselaer Polytechnic Institute Frank Henkel. IMST Chun-Ming Hsu, IBM Tian-Wei Huang, National Taiwan University Gernot Hueber, NXP Semiconductors Nobuyuki Itoh, Okayama Prefectural University Reynold Kagiwada, Northrop Grumman Waleed Khalil, Obio State University Jaber Khoja, Qualcomm Savfe Kiaei, Arizona State University Bumman Kim, POSTECH Jennifer Kitchen, Arizona State University Eric Klumperink, University of Twente Kevin Kobayashi, RFMD Harish Krishnaswamy, Columbia University

Youngwoo Kwon, Seoul National University Fred Lee, Fairchild Semiconductor Tzung-Yin Lee, Skyworks Solutions Chang-Ho Lee, Oualcomm Domine Leenaerts, NXP Semiconductors Salvatore Levantino. Politecnico di Milano Donald Y.C. Lie, Texas Tech University Jenshan Lin, University of Florida Li Lin, Marvell Technology Group Fujiang Lin, USTC Danilo Manstretta, University of Pavia Mozhgan Mansuri, Intel Srenik Mehta, Qualcomm Mohyee Mikhemar, Broadcom Pedram Mohseni, Case Western Reserve University Jyoti Mondal, Northrop Grumman Arun Natarajan, Oregon State University Kenjiro Nishikawa, Kagoshima University Jeyanandh Paramesh, Carnegie Mellon University Stefano Pellerano, Intel Dennis Poulin, Anritsu Company Madhukar Reddy, MaxLinear Francois Rivet, University of Bordeaux Francis Rotella, Peregrine Semiconductor Chris Rudell, University of Washington Derek Shaeffer. InvenSense Osama Shanaa, MediaTek Eddie Spears, RFMD R. Bogdan Staszewski, Delft University of Technology Joseph Staudinger, Freescale Semiconductor Bob Stengel, SiriusXM Noriharu Suematsu, Toboku University Julian Tham, Broadcom Steven Turner, BAE Systems Leon van den Oever, Radio Semiconductor Freek van Straten. NXP Semiconductors Jeffrey Walling, University of Utab Yanjie Wang, Intel Hua Wang, Georgia Institute of Technology David Wentzloff. University of Michigan Magnus Wiklund, Qualcomm Atheros James Wilson, US Army Research Laboratory Renaldi Winoto, Marvell Semiconductor Haolu Xie. ZTE USA Li-Wu Yang, Jiao-Tong University Chen Yang, University of California at Berkeley Patrick Yue. HKUST Gary Zhang, Skyworks Solutions

# **RFIC 2014 Schedule**

#### Saturday, 31 May 2014

08:00–18:00 Registration — Tampa Convention Center (TCC) 2<sup>nd</sup> Lobby

#### Sunday, 1 June 2014

- 07:00–19:00 Registration TCC 2<sup>nd</sup> Lobby

- 07:00–08:00 Speakers' Breakfast TCC Ballroom A

- 07:00–08:00 Ŵorkshop Breakfast TCC Ballroom D

- 08:00-17:00 Workshops and Short Courses, TCC 10-25

- 12:00–13:00 Workshops Lunch TCC Ballroom D

- 17:30–19:00 RFIC Plenary Marriott Grand Ballroom

- 19:00-20:00 Industry Showcase and Reception Part 1 Marriott Grand Ballroom Foyer

- 20:00–21:00 RFIC Plenary Roundtable Marriott Grand Ballroom

- 21:00–22:00 Reception Part 2 Marriott Grand Ballroom Foyer

#### Monday, 2 June 2014

- 07:00–19:00 Registration TCC 2<sup>nd</sup> Lobby

- 07:00–08:00 Speakers' Breakfast TCC Ballroom A

- 07:00–08:00 Workshop Breakfast TCC Ballroom D

- 08:00-17:00 Workshops and Short Courses TCC 10-25

- 08:00–09:40 RM01A TCC 10–11: Energy-Efficient Wireless Transceivers

- RM01B TCC 13–14: Blocker-Tolerant and Low-Noise Front-Ends

- 09:40-10:10 Break

- 10:10–11:50 RMO2A TCC 10–11: Mixed Signal Circuits at Gigabertz Frequencies RMO2B — TCC 13–14: K-Band Front-End ICs RMO2C — TCC 15–16: Advanced PLL Techniques

RMO2D — TCC 18: Advancements in Distributive, Thermal, and Non-Linear Device Modeling

- 12:00–13:00 Workshops Lunch TCC Ballroom D

- 12:00–13:30 RFIC Panel TCC Ballroom A

- 13:00–14:30 RFIC Steering Committee Lunch Meeting Marriott Florida Salon 4–5

- 13:30–15:10 RMO3A TCC 10–11: Advances in Wireless Mobile ICs RMO3B — TCC 13–14: mm-Wave PAs: 60GHz and Beyond

- RM03C TCC 15–16: mm-Wave & Terabertz Frequency Generation Techniques RM03D — TCC 18: Advances in Nano-Scale Devices and Novel Measurement Techniques for RFIC Designs

- Techniques for KFIC De

- 15:10–15:40 Break

- 15:40–17:20 RMO4A TCC 10–11: Wireless Connectivity Transceivers and Multi-Standard Digital Transmitters

- RMO4B TCC 13–14: *Highly-Efficient Power Amplifiers*

- RMO4C TCC 15-16: Quadrature and Multi-Mode VCOs

- RMO4D TCC 18: High-Speed Data Transceivers

#### Tuesday, 3 June 2014

- 07:00–19:00 Registration TCC 2<sup>nd</sup> Lobby

- 07:00-08:00 Speakers' Breakfast TCC Ballroom A

- 08:00-09:40 RTU1C TCC 15-16: mm-Wave Integration Technologies

- 09:40-10:10 Break

- 10:10–11:50 RTU2A TCC 10–11: Software-Defined and Cognitive Radio Techniques RTU2B — TCC 13–14: Multiband PAs and Power Mixers RTU2C — TCC 15–16: Sub-mm-Wave Transceivers

- 12:00–13:30 RFIC Panel TCC Ballroom B

- 13:00–14:30 RFIC TPC Lunch Meeting Marriott Florida Salon 4–5

- 13:30-16:00 RTUIF ---- TCC Ballroom C-D: Interactive Forum

# Plenary, Round-Table, Industry Showcase, and Reception Schedule

#### Sunday Evening, 1 June 2014 Marriott Waterside Hotel and Marina

#### 1**7:30**

## Marriott Grand Ballroom RFIC Plenary

# Chair: Lawrence Kushner, BAE Systems Co-Chair: Bertan Bakkaloglu, Arizona State University Co-Chair: Albert Wang, University of California at Riverside

- 17:30 Welcome Message from General and TPC Chairs, Student Paper Awards

- 18:00 *How to differentiate with RF Silicon Technologies in high volume applications?* Pieter Hooijmans, NXP Semiconductors

- 18:30 The Next Era of Wireless Communications Enabling Revolutions in Health Care, Transportation, Energy, and the Environment Lawrence Larson, Brown University

#### **19:00**

#### Marriott Grand Ballroom Foyer "Hot Chips and Cold Drinks" Industry Showcase and Reception Part 1

#### 20:00

## Marriott Grand Ballroom The Inaugural RFIC Plenary Round Table

Organizer and Moderator:

Hossein Hashemi, University of Southern California

Participants:

Zdravko Boos, Intel Peter L. Gammel, Skyworks Solutions Pieter Hooijmans, NXP Semiconductors Lawrence Larson, Brown University Reza Rofougaran, Broadcom Kamal Sahota, Qualcomm

#### 21:00 Marriott Grand Ballroom Foyer Reception Part 2

# **Student Paper Award Finalists**

One of the missions of RFIC Symposium is to encourage academic research and education. Best Student Award finalists nominated every year by RFIC Technical Program Committee benefit from a free RFIC registration. Among these, three Best Student Papers are further selected and awarded a \$500 honorarium during the plenary session. This year's best student finalists are:

- A 2.5nJ/Bit Multiband (MBAN & ISM) Transmitter for IEEE 802.15.6 Based on a Hybrid Polyphase-MUX/ILO Based Modulator Mustafijur Rahman, Mohammad Elbadry, Ramesh Harjani University of Minnesota, USA RMO1A-2 08:20A Low-Power Digitally Controlled Wideband FM Transceiver N. Saputra<sup>1</sup>, John R. Long<sup>1</sup>, John J. Pekarik<sup>2</sup> <sup>1</sup>Technische Universiteit Delft, The Netherlands, <sup>2</sup>IBM, USA RMO1A-3 08:40A Compact 24–54GHz CMOS Band-Pass Distributed Amplifier for High Fractional Bandwidth Signal Amplification V. Bhagavatula<sup>1</sup>, M. Taghivand<sup>2</sup>, Jacques C. Rudell<sup>1</sup> <sup>1</sup>University of Washington, USA, <sup>2</sup>Qualcomm, USA RMO2B-1 10:10

- A 0.6/1.2-V 14.1-mW 96.8GHz-to-108.5GHz Transformer-Based PLL with Embedded Phase Shifter in 65-nm CMOS

Yue Chao<sup>1</sup>, Howard C. Luong<sup>1</sup>, Zhiliang Hong<sup>2</sup>

<sup>1</sup>HKUST, China, <sup>2</sup>Fudan University, China RM02C-2 10:30

A Circuit-Level Model for Accurately Modeling 3rd Order Nonlinearity in CMOS Passive Mixers Hazal Yüksel, Dong Yang, Alyosha C. Molnar Cornell University, USA RMO2D-5 11:30

Broadband CMOS Stacked Power Amplifier Using Reconfigurable Interstage Network for Envelope Tracking Application

Sunghwan Park, Jung-Lin Woo, Moon-Suk Jeon, Unha Kim, Youngwoo Kwon

Seoul National University, Korea

RM03A-4 14:30

Spatially Power-Combined W-Band Power Amplifier Using Stacked CMOS

Jefy Jayamon, Ozan Gurbuz, Bassel Hanafi, Amir Agah, James Buckwalter, Gabriel M. Rebeiz,

Peter Asbeck

University of California at San Diego, USA

RM03B-1

13:30

A High-Power, Low-Loss W-Band SPDT Switch Using SiGe PIN Diodes Peter Song, Robert L. Schmid, Ahmet Çağrı Ulusoy, John D. Cressler Georgia Institute of Technology, USA RM03D-2 13:50

#### Sunday, 1 June 2014

#### 17:30-18:00

**Marriott Grand Ballroom**

| <ul> <li>A +27.3dBm Transformer-Based Digital Doherty Polar Power Amplifier Fully Integrated in<br/>Bulk CMOS</li> <li>Song Hu<sup>1</sup>, Shouhei Kousai<sup>2</sup>, Jong Seok Park<sup>1</sup>, Outmane Lemtiri Chlieh<sup>1</sup>, Hua Wang<sup>1</sup></li> <li><sup>1</sup>Georgia Institute of Technology, USA, <sup>2</sup>Toshiba Corporation, Japan</li> <li>RMO4B-2</li> <li>16:00</li> </ul> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A 26-GHz Low-Phase-Error In-Phase-Coupled QVCO Using Modified Bi-Directional Diodes<br>Jun-Chau Chien, Nai-Chung Kuo, Ali M. Niknejad<br>University of California at Berkeley, USA<br>RMO4C-1 15:40                                                                                                                                                                                                       |

| A 2.75–6.25GHz Low-Phase-Noise Quadrature VCO Based on a Dual-Mode Ring Resonator in<br>65nm CMOS<br>Masoud Moslehi Bajestan, Vahid Dabbagh Rezaei, Kamran Entesari<br>Texas A&M University, USA<br>RMO4C-4 16:40                                                                                                                                                                                         |

| A 3-mW 25-Gb/s CMOS Transimpedance Amplifier with Fully Integrated Low-Dropout<br>Regulator for 100GbE Systems<br>Yipeng Wang, Yan Lu, Quan Pan, Zhengxiong Hou, Liang Wu, Wing-Hung Ki, C. Patrick Yue<br>HKUST, China<br>RMO4D-2 16:00                                                                                                                                                                  |

| Dynamic Polarization Control of Integrated Radiators<br>Steven M. Bowers, Amirreza Safaripour, Ali Hajimiri<br>California Institute of Technology, USA<br>RTU1C-1 08:00                                                                                                                                                                                                                                   |

| A 79-GHz Bidirectional Pulse Radar System with Injection-Regenerative Receiver in 65nm<br>CMOS<br>Pen-Jui Peng, Chiro Kao, Chin-Yang Wu, Jri Lee<br>National Taiwan University, Taiwan<br>RTU1C-4 09:00                                                                                                                                                                                                   |

| A Widely Tunable Active Duplexing Transceiver with Same-Channel Concurrent RX/TX and<br>30dB RX/TX Isolation<br>Dong Yang, Alyosha C. Molnar<br>Cornell University, USA<br>RTU2A-3 10:50                                                                                                                                                                                                                  |

| A 1.8dB NF Blocker-Filtering Noise-Canceling Wideband Receiver with Shared TIA in 40nm<br>CMOS<br>Hajir Hedayati <sup>1</sup> , Wing-Fat Andy Lau <sup>2</sup> , Namsoo Kim <sup>2</sup> , Vladimir Aparin <sup>2</sup> , Kamran Entesari <sup>1</sup><br><sup>1</sup> Texas A&M University, USA, <sup>2</sup> Qualcomm, USA                                                                              |

RTU2A-4 11:10

# **Plenary Speaker 1**

#### Pieter Hooijmans Vice President R&D and Strategy NXP Semiconductors

How to Differentiate with RF Silicon Technologies in High Volume Applications?

**Abstract:** The presentation will start with an overview of functional and technology mapping of RF systems, ranging from RF amplifiers to System-on-Chips (SoC's), and from modules to Wafer-Level Chip-Scale Packaging (WLCSP).

We'll then discuss why (dedicated) Si-based component technologies are very price-performance competitive in volume markets, namely a combination of low-cost manufacturing in large volume Si fabs., as well as the right integration level.

Three RF application segments will be illustrated, including cellular and microwaves, and it will be shown how the technologies are applied for optimal solutions.

#### **About Pieter Hooijmans**

Pieter Hooijmans, currently Vice President R&D and Strategy for one of the five Business units of NXP Semiconductors from Eindhoven, the Netherlands, has spent a more than 25 year career in and around RF.

After an MSc and PhD (cum laude) in microwave and communication technology at the Technical University Delft, as well as a period as radar specialist with the Royal Netherlands Air Force, he started a long career with Philips Research, Philips Consumer Electronics, and finally Philips Semiconductors which became NXP in 2006. In these years he has covered a very broad range of RF applications, ranging from radio, TV and satellite reception, high speed optical storage, mobile and cordless phones, base stations and infrastructure, to today's Internet-of-Things.

Current activities include, next to other domains, driving technology and platform roadmaps for Base Station RF PA's, Wireless Connectivity Front ends, Si Tuners and low power RF (Zigbee and BTLE) for the Internet-of-Things.

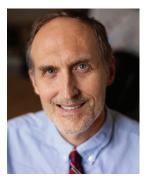

# **Plenary Speaker 2**

#### Lawrence Larson Founding Dean of the School of Engineering Brown University

#### The Next Era of Wireless Communications — Enabling Revolutions in Health Care, Transportation, Energy, and the Environment

**Abstract:** 2013 marked the 40th anniversary of the first cellular telephone call. The growth of personal portable wireless communications since then has created a global communications network unprecedented in human history. This anniversary gives us the opportunity to consider what the next forty years of wireless communication might look like. Further inevitable Improvements in semiconductor technology, with resulting improvements in processing power, transistor speed and complexity will result in exciting new applications of wireless devices.

Wireless technology has historically been focused on personal or data communications, but some of the most exciting new approaches will center on medical, energy, transportation and environmental applications. These include such areas as wireless medical and neural interfaces, networked personal transportation and infrastructure, and the "internet of things."

This talk will summarize the emerging wireless technologies that will enable these new applications, and present some of the challenges to their widespread adoption.

#### About Lawrence Larson

Larry Larson received the BS in Electrical Engineering from Cornell University and a PhD from UCLA. From 1980–1996 he was at Hughes Research Laboratories in Malibu, CA, where he developed high-frequency microelectronics in GaAs, InP and Si/SiGe and MEMS technologies. He joined the faculty at the University of California at San Diego, in 1996, where he was the inaugural holder of the Communications Industry Chair. He was Director of the UCSD Center for Wireless Communications from 2001–2006 and was Chair of the Department of Electrical and Computer Engineering from 2007–2011.

He moved to Brown University in 2011, where he is Founding Dean of the School of Engineering. He was recipient of the Hughes Sector Patent Award in 1994 for his work on RF MEMS, co-recipient of the 1996 Lawrence A. Hyland Patent Award of Hughes Electronics, for his work on low-noise millimeterwave HEMTs, co-recipient of the 1999 IBM Microelectronics Excellence Award for his work in Si/SiGe HBT technology and co-recipient of the CICC Best Invited Paper Award in 2005. He has published over 300 papers, received over 40 US patents, co-authored four books, and is a Fellow of the IEEE.

# "Hot Chips and Cold Drinks" Industry Showcase

#### Chair: Bob Stengel, SiriusXM

This year for the first time, the most innovative and highly-rated industrial papers will be highlighted in the Industry Showcase, held concurrently with the plenary reception. Authors of these papers will be present to discuss their work, summarized in poster format. Media will be present to cover this event, making it an excellent opportunity to announce the latest RFIC developments and breakthroughs. This year's Industry Showcase papers are:

| A 5 <sup>th</sup> Order 0.8/2.4GHz Programmable Active Band Pass Filter for Power DAC Applications<br>HRL Laboratories, USA                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Zhiwei Xu, Deborah Winklea, Thomas C. Oh, Samuel Kim, Steven T.W. Chen, Yakov Royter, Maggy Lau, Irma Valles,                                                                                                                                                          |

| Donald A. Hitko, James C. Li                                                                                                                                                                                                                                           |

| RM02A-1 10:10                                                                                                                                                                                                                                                          |

| A 9.2–12.7GHz Wideband Fractional-N Subsampling PLL in 28nm CMOS with 280fs RMS                                                                                                                                                                                        |

| Jitter                                                                                                                                                                                                                                                                 |

| imec, Belgium<br>Kuba Raczkowski, Nereo Markulic, Benjamin Hershberg, Joris Van Driessche, Jan Craninckx                                                                                                                                                               |

| RM02C-1 10:10                                                                                                                                                                                                                                                          |

| Variable Delay Transmission Lines in Advanced CMOS SOI Technology                                                                                                                                                                                                      |

| <sup>1</sup> IBM, Israel, <sup>2</sup> IBM, USA                                                                                                                                                                                                                        |

| Shlomo Shlafman <sup>1</sup> , Benny Sheinman <sup>1</sup> , Danny Elad <sup>1</sup> , Alberto Valdes-Garcia <sup>2</sup> , Mihai A.T. Sanduleanu <sup>2</sup><br>RMO2D-1 10:10                                                                                        |

| A HSPA+/WCDMA/EDGE 40nm Modem SoC with Embedded RF Transceiver Supporting RX                                                                                                                                                                                           |

| Diversity                                                                                                                                                                                                                                                              |

| <sup>1</sup> MediaTek, UK, <sup>2</sup> MediaTek, Taiwan, <sup>3</sup> MediaTek, Singapore, <sup>4</sup> MediaTek, USA                                                                                                                                                 |

| Jon Strange <sup>1</sup> , Hsiang-Hui Chang <sup>2</sup> , Paul Muller <sup>1</sup> , Walid Ali-Ahmad <sup>3</sup> , Christophe Beghein <sup>1</sup> , Fahd Ben Abdeljelil <sup>1</sup> ,                                                                              |

| Wen-Chang Lee <sup>2</sup> , Charles Chiu <sup>2</sup> , Tze Yee Sin <sup>3</sup> , Ta-Hsin Lin <sup>2</sup> , David Ivory <sup>1</sup> , Hao-Tang Shih <sup>2</sup> , Chris Beale <sup>1</sup> ,                                                                      |

| Dimitris Nalbantis <sup>1</sup> , Ivan S.C. Lu <sup>4</sup> , Chi-Wei Fan <sup>2</sup> , Shao-Hung Lin <sup>2</sup> , Hsin-Hua Chen <sup>2</sup> , Chih-Hao Sun <sup>2</sup> , Li-Shin Lai <sup>2</sup> ,<br>Jhy-Rong Chen <sup>2</sup> , Sheng-Jui Huang <sup>2</sup> |

| RMO3A-1 13:30                                                                                                                                                                                                                                                          |

| A Multiband Power Amplifier Using Combination of CMOS and GaAs Technologies for WCDMA                                                                                                                                                                                  |

| Handsets                                                                                                                                                                                                                                                               |

| Mitsubishi Electric Corporation, Japan                                                                                                                                                                                                                                 |

| T. Shimura, S. Maki, S. Fujiwara, K. Fujii, Y. Takahashi, S. Suzuki, M. Miyashita, K. Yamamoto, H. Seki, M. Hieda,                                                                                                                                                     |

| Y. Hirano                                                                                                                                                                                                                                                              |

| RM03A-3 14:10                                                                                                                                                                                                                                                          |

| A 46.4–58.1GHz Frequency Synthesizer Featuring a 2nd Harmonic Extraction Technique                                                                                                                                                                                     |

| That Preserves VCO Performance                                                                                                                                                                                                                                         |

| IBM, USA                                                                                                                                                                                                                                                               |

| Bodhisatwa Sadhu, Mark Ferriss, Alberto Valdes-Garcia<br>RMO3C-1 13:30                                                                                                                                                                                                 |

| mm-Wave Noise Characterization of 40nm CMOS Transistor for up to 67GHz                                                                                                                                                                                                 |

| <sup>1</sup> GLOBALFOUNDRIES, Singapore, <sup>2</sup> Focus Microwaves, Canada                                                                                                                                                                                         |

| Xi Sung Loo <sup>1</sup> , Hoang V. Nguyen <sup>2</sup> , Zhihong Liu <sup>1</sup> , Johnny Kok Wai Chew <sup>1</sup> , Neven Misljenovic <sup>2</sup> , Bryan Hosein <sup>2</sup> ,                                                                                   |

| Christos Tsironis <sup>2</sup> , Jen Shuang Wong <sup>1</sup> , Wai Heng Chow <sup>1</sup>                                                                                                                                                                             |

| RM03D-1 13:30                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                        |

Sunday, 1 June 2014

#### 19:00–20:00 Marriott Grand Ballroom Foyer

*RF Power Transistor Characterization and Testing with Hybrid Harmonic Injection Source and Load Tuners*

Focus Microwaves, Canada Hoang V. Nguyen, Neven Misljenovic, Bryan Hosein RMO3D-5 14:50

- A 55nm CMOS 4-in-1 (11b/g/n, BT, FM, and GPS) Radio-in-a-Package with IPD Front-End Components Directly Connected to Antenna <sup>1</sup>MediaTek, Taiwan, <sup>2</sup>MediaTek, Singapore, <sup>3</sup>MediaTek, USA Jing-Hong Conan Zhan<sup>1</sup>, Yuli Hsueh<sup>1</sup>, Min Chen<sup>1</sup>, Meng-Hsiung Hung<sup>1</sup>, Yi-An Li<sup>1</sup>, Lan-Chou Cho<sup>1</sup>, Hui-Hsien Liu<sup>1</sup>, Ming-Da Tsai<sup>1</sup>, Ping-Yu Chen<sup>1</sup>, Jui-Lin Syu<sup>1</sup>, Yi-Chien Tsai<sup>1</sup>, Tao-Yao Chang<sup>1</sup>, Jen-Che Tsai<sup>1</sup>, Sheng-Hao Chen<sup>1</sup>, Ping-Hsuan Tsu<sup>1</sup>, Kuo-Hao Chen<sup>1</sup>, Chun-Yi Wu<sup>1</sup>, Sheng Jau Wong<sup>2</sup>, Chun Geik Tan<sup>2</sup>, George Chien<sup>3</sup> RMO4A-1 15:40

- A 23dBm Fully Digital Transmitter Using  $\Sigma\Delta$  and Pulse-Width Modulation for LTE and WLAN Applications in 45nm CMOS

Texas Instruments, USA Rahmi Hezar, Lei Ding, Joonhoi Hur, Baher Haroun RMO4A-3 16:20

A 2×2 MIMO 802.11abgn/ac WLAN SoC with Integrated T/R Switch and On-Chip PA Delivering VHT80 256QAM 17.5dBm in 55nm CMOS <sup>1</sup>MediaTek, Taiwan, <sup>2</sup>MediaTek, USA

Tsung-Ming Chen<sup>1</sup>, Wei-Chia Chan<sup>1</sup>, Chien-Cheng Lin<sup>1</sup>, Jui-Lin Hsu<sup>1</sup>, Wen-Kai Li<sup>1</sup>, Pi-An Wu<sup>1</sup>, Yen-Lin Huang<sup>1</sup>, Yen-Chuan Huang<sup>1</sup>, TzungChuen Tsai<sup>1</sup>, Po-Yu Chang<sup>1</sup>, Chih-Lung Chen<sup>1</sup>, Chih-Hou Tsai<sup>1</sup>, Tao-Yao Chang<sup>1</sup>, I-Ching Huang<sup>1</sup>, Wen-Hsien Chiu<sup>1</sup>, Chun-Hao Liao<sup>1</sup>, Chia-Hsin Wu<sup>1</sup>, George Chien<sup>2</sup> RMO4A-5 17:00

A 25dBm Outphasing Power Amplifier with Novel Non-Isolated Combining Network Texas Instruments, USA

Lei Ding, Joonhoi Hur, Rahmi Hezar, Baher Haroun RMO4B-1 15:40

A 2.4GHz Class-D Power Amplifier with Conduction Angle Calibration for -50dBc Harmonic Emissions

<sup>1</sup>imec, The Netherlands, <sup>2</sup>Renesas Electronics Corporation, Japan, <sup>3</sup>Technische Universiteit Delft, The Netherlands

Ao Ba<sup>1</sup>, Vamshi Krishna Chillara<sup>1</sup>, Yao-Hong Liu<sup>1</sup>, Hiromu Kato<sup>2</sup>, Kathleen Philips<sup>1</sup>, Robert Bogdan Staszewski<sup>3</sup> RMO4B-3 16:20

A Compact Antenna-in-Package 60-GHz SiGe BiCMOS Radio

Peraso Technologies, Canada

Eric Juntunen, Alex Tomkins, Alan Poon, Jennifer Pham, Ahmed El-Gabaly, Mohammad Fakharzadeh, Hatem Tawfik, Yat-Loong To, Mihai Tazlauanu, Brad Lynch, Ron Glibbery

RMO4D-5 17:00

A 64QAM 94GHz CMOS Transmitter SoC with Digitally-Assisted Power Amplifiers and Thru-Silicon Waveguide Power Combiners

<sup>1</sup>Northrop Grumman Aerospace Systems, USA, <sup>2</sup>Space Micro, USA, <sup>3</sup>University of California at Los Angeles, USA

Tim LaRocca<sup>1</sup>, Yi-Cheng Wu<sup>1</sup>, Khanh Thai<sup>1</sup>, Rob Snyder<sup>1</sup>, Naveen Daftari<sup>1</sup>, Owen Fordham<sup>1</sup>, Paul Rodgers<sup>2</sup>, Monte Watanabe<sup>1</sup>, Yeat Yang<sup>1</sup>, Mohammad Ardakani<sup>1</sup>, Waleed Namoos<sup>1</sup>, Sumiko Poust<sup>1</sup>, Mau-Chung Frank Chang<sup>3</sup> RTU1C-2 08:20

A Multi-Mode Software-Defined CMOS BPSK Receiver SoC for the Newly Enhanced WWVB Atomic Clock Broadcast

Xtendwave, USA

O. Eliezer, T. Jung, R. Lobo, M. Appel, Y. Liang, D. Robbins, P. Nelsen, Z. Islam

RTUIF-3 13:30

#### Sunday, 1 June 2014

#### 19:00–20:00 Marriott Grand Ballroom Foyer

# **Round Table Discussion**

#### **Beyond 4G Wireless Communications: An RFIC Perspective**

Organizer and Moderator:

Hossein Hashemi, Associate Professor, University of Southern California

Participants:

Zdravko Boos Fellow Intel

Peter L. Gammel Chief Technology Officer Skyworks Solutions

Pieter Hooijmans Vice President R&D and Strategy NXP Semiconductors

Reza Rofougaran Senior Vice President Engineering & Fellow Vice President Engineering Broadcom

Lawrence Larson Dean, School of Engineering Brown University

Kamal Sahota Qualcomm

Sunday, 1 June 2014

20:00-21:00

#### Marriott Grand Ballroom

## Monday, 2 June 2014 08:00–09:40 Room TCC 10–11 Session RM01A: Energy-Efficient Wireless Transceivers Chair: David Wentzloff, University of Michigan Co-Chair: Gernot Hueber, NXP Semiconductors

## RM01A-1 08:00

# A 2.3pJ/Bit Frequency-Stable Impulse OOK Transmitter Powered Directly by an RF Energy Harvesting Circuit with -19.5dBm Sensitivity

Hiroyuki Ito<sup>1</sup>, Shoichi Masui<sup>2</sup>, Youichi Momiyama<sup>2</sup>, Atsushi Shirane<sup>1</sup>, Motohiro Takayasu<sup>1</sup>, Yoshihiro Yoneda<sup>1</sup>, Taiki Ibe<sup>1</sup>, Taisuke Hamada<sup>1</sup>, Sho Ikeda<sup>1</sup>, Daisuke Yamane<sup>1</sup>, Noboru Ishihara<sup>1</sup>, Kazuya Masu<sup>1</sup>; <sup>1</sup>Tokyo Institute of Technology, Japan, <sup>2</sup>Fujitsu Laboratories, Japan

**Abstract:** The proposed 2.5-GHz-band impulse transmitter technology realizes frequency-stable impulse generation against PVT variation and superior energy-per-bit operation, and it can be powered directly from a -19.5-dBm-sensitivity RF energy harvesting circuit without any regulators that are generally essential to power RF circuits. The transmitter occupies 0.38 mm<sup>2</sup> in a 65nm CMOS technology. The maximum frequency difference among measured output return-loss peak of 9 chips with 3 different process corners under 0.5 V supply is about 50 MHz without any frequency calibration. Our prototype achieves 1 Mb/s signal transmission under 2.3  $\mu$ W power consumption from 0.5 V supply thanks to pulse-level duty cycling operation of maximally digital architecture.

# RM01A-2 08:20

#### A 2.5nJ/Bit Multiband (MBAN & ISM) Transmitter for IEEE 802.15.6 Based on a Hybrid Polyphase-MUX/ILO Based Modulator

Mustafijur Rahman, Mohammad Elbadry, Ramesh Harjani; University of Minnesota, USA

**Abstract:** This paper describes a 802.15.6 compliant 2360–2484MHz multiband transmitter that digitally multiplexes the appropriate phases from an 800MHz poly-phase filter output to generate  $\pi/4$  DQPSK signals at 2.4GHz. Modulation at  $1/3^{rd}$  the RF frequency reduces the transmitter power consumption and enables channel selection using a PLL running at 800MHz. The prototype transmitter consumes 2.4mW while delivering -10dBm RF power at the TX output resulting in an energy efficiency of 2.5nJ/bit at 1.2Mbps. The measured RMS EVM for  $\pi/4$  DQPSK modulation is 3.21%.

#### RM01A-3 08:40

#### A Low-Power Digitally Controlled Wideband FM Transceiver

N. Saputra<sup>1</sup>, John R. Long<sup>1</sup>, John J. Pekarik<sup>2</sup>; <sup>1</sup>Technische Universiteit Delft, The Netherlands, <sup>2</sup>IBM, USA

**Abstract:** A frequency-agile, low-power 3–5GHz FM transceiver with on-chip calibration, and digital control of Rx gain, Tx power, and carrier frequency is described. The FCC-compliant transmitter incorporates a 3-phase CCO and frequency-tripling PA. A tunable LNA, envelope detector, limiter, and FSK demodulator comprise the receiver. Measured Rx sensitivity is -80.5dBm (10<sup>-3</sup> BER) at 100kb/s.

The  $0.9mm^2$  IC fabricated in 90nm RF-CMOS dissipates  $630\mu\text{W}$  in Tx and  $580\mu\text{W}$  in Rx mode from a 1V supply.

# RMO1A-4 09:00

# A 700pJ/Bit, 2.4GHz, Narrowband, PLL-Free Burst Mode Transmitter Based on an FBAR with 5µs Startup Time for Highly Duty-Cycled Systems

Raghavasimhan Thirunarayanan<sup>1</sup>, David Ruffieux<sup>2</sup>, Franz Pengg<sup>2</sup>, Nicola Scolari<sup>2</sup>, Pascal Persechini<sup>2</sup>, Christian Enz<sup>1</sup>; <sup>1</sup>EPFL, Switzerland, <sup>2</sup>CSEM, Switzerland

**Abstract:** This paper presents a PLL-free transmitter based on an FBAR achieving a 5µs startup time to reduce the crystal oscillator power overhead which degrades the energy efficiency for heavily duty cycled systems. The TX upconverts a FSK-modulated FBAR DCO signal with the IF output of a Phase Switching Divider (PSD) injection locked to the DCO. The PSD has a division step of 0.2 to circumvent the limited FBAR tuning range that prevents addressing all the channels in the various bands between 2.36 and 2.5 GHz. Integrated in a 65nm technology, the TX outputs -1dBm and consumes 9.2mA at 1.2V. Further, the TX is capable of data rates up to 16 Mbps leading to a peak energy efficiency of 700pJ/b as well as a multi-fold reduction in the mean power dissipation at lower mean data rates.

# RM01A-5 09:20

# A 0.5-V 5.8-GHz Ultra-Low-Power RF Transceiver for Wireless Sensor Network in 65nm CMOS

Sho Ikeda, Sang-yeop Lee, Shin Yonezawa, Yiming Fang, Motohiro Takayasu, Taisuke Hamada, Yosuke Ishikawa, Hiroyuki Ito, Noboru Ishihara, Kazuya Masu; Tokyo Institute of Technology, Japan

**Abstract:** This paper proposes the RF CMOS transceiver that is suitable for wireless sensor network applications. To reduce the size of the antenna, target frequency is chosen to be 5.8GHz band, therefore proposed transceiver has potentiality to achieve ultra-small size wireless sensor module. Supply voltage of 0.5V can reduce the power consumption of overall RF transceiver. Current-reuse VCO and injection-locked frequency divider can enable ultra-low-power consumption of the PLL. In order to achieve both low power and high sensitivity, uncertain-IF and active mixer first architecture of the receiver are employed. Inverter-based topology of the transmitter is suitable for low supply voltage.

The prototype transceiver was fabricated in 65nm CMOS process, and the transmitter achieved EVM of 12.6% while consuming 2.86mW including the PLL, and the receiver realizes sensitivity of -75dBm while consuming 0.83mW including the local oscillator.

## Monday, 2 June 2014 08:00–09:40 Room TCC 13–14 Session RMO1B: Blocker-Tolerant and Low-Noise Front-Ends Chair: Domine Leenaerts, NXP Semiconductors Co-Chair: Frank Henkel, IMST

#### RM01B-1 08:00 A Noise Cancelling 0.7–3.8GHz Resistive Feedback Receiver Front-End in 65nm CMOS

Anders Nejdel, Markus Törmänen, Henrik Sjöland; Lund University, Sweden

**Abstract:** This paper presents a noise cancelling 0.7–3.8GHz receiver front-end implemented in 65nm technology. The circuit has a main path consisting of a high input impedance  $g_m$ -stage, current-mode passive mixers and baseband amplifiers, where the input match is provided by frequency translational negative feedback from baseband to RF input. An auxiliary path with tunable gain is introduced to cancel noise from the main path while maintaining linearity. The receiver front-end achieves a noise figure of 1.6–3.7dB and an IIP2 and IIP3 of >75dBm and >1dBm, respectively. The current consumption of the circuit is 22.8–34.9mA, from a 1.2V supply.

# RM01B-2 08:20

A Blocker-Tolerant RF Front End with Harmonic-Rejecting N-Path Filtering

Yang Xu, Jianxun Zhu, Peter R. Kinget; Columbia University, USA

**Abstract:** A 0.2–1GHz RF front end with a harmonic-rejecting N-path filter (HR-NPF) features tunable narrow band filtering as well as high attenuation at the 3rd and 5th order LO harmonics at the LNA output. The B1dB-CP is -2.4dBm at a 20MHz offset, and remains high at the 3rd and 5th LO harmonics thanks to the HR-NPF configuration. The reverse isolation of the LNA helps to keep the LO emission below -90dBm. The two-stage harmonic rejection approach offers >51dB harmonic rejection ratio at the 3rd and 5th LO harmonics without calibration. The front end consumes 26–32mA while occupying an area of 0.77mm<sup>2</sup>.

# RM01B-3 08:40

# An Integrated CMOS Passive Transmitter Leakage Suppression Technique for FDD Radios

Tong Zhang, Apsara Ravish Suvarna, V. Bhagavatula, Jacques C. Rudell; University of Washington, USA

**Abstract:** An integrated passive transmitter (TX) leakage suppression technique is proposed for FDD Radios. A Four Port Canceller (FPC) serves a dual function as a receiver (RX) input matching network, and provides an auxiliary path from TX to RX, used for leakage cancellation, without degrading the RX noise figure (NF). The FPC is integrated with a low noise amplifier (LNA) and an emulated power amplifier (PA) in 40nm CMOS process. A cancellation of 23dB is achieved with a negligible power consumption and noise penalty.

# RMO1B-4 09:00

## A 2-Stage Recursive Receiver Optimized for Low Flicker Noise Corner

Rangakrishnan Srinivasan, Wei-Gi Ho, Travis Forbes, Ranjit Gharpurey; University of Texas at Austin, USA

**Abstract:** Multi-frequency signal recursion allows for efficient reuse of transconductance in a radio receiver, which helps to reduce power dissipation. An I-Q receiver based on the recursive principle is demonstrated here. The design employs a self-biased load, with chopping at baseband in order to minimize low-frequency in-band flicker noise. The bias setting of the chopper devices is optimized to enhance the baseband load impedance and conversion gain of the receiver. An implementation in 130 nm CMOS provides 59.6 dB conversion gain for an RF of 960 MHz, and 8.2 dB DSB-NF. The measured flicker noise corner frequency is 100 kHz. The total current requirement is 2.6 mA from a 1.2 V supply.

## RMO1B-5 09:20

#### In-situ Noise Characterization of a 20–35GHz 32nm SOI CMOS Reconfigurable LNA Using a Broadband On-Chip Noise Source

Mohammad Ghadiri-Sadrabadi, Ajay Subramanian, Ahmet H. Coskun, Joseph C. Bardin; University of Massachusetts at Amherst, USA

**Abstract:** A novel broadband current-mode noise source implemented in 32 nm SOI CMOS and appropriate for the in-situ testing of wide-band mm-wave low noise amplifiers is presented. The noise source was used to characterize a 20–35 GHz low noise amplifier and it was found that the noise source ENR is sufficiently repeatable to enable accurate noise measurements without the individual calibration of each integrated circuit. To the authors' knowledge, this work represents the first time that a CMOS integrated noise source has been used to characterize the noise performance of a mm-wave amplifier.

# Monday, 2 June 2014 10:10-11:50 Room TCC 10-11

#### Session RMO2A: Mixed Signal Circuits at Gigahertz Frequencies Chair: Jennifer Kitchen, Arizona State University Co-Chair: Renaldi Winoto, Marvell Semiconductors

#### RM02A-1 10:10 A 5<sup>th</sup> Order 0.8/2.4GHz Programmable Active Band Pass Filter for Power DAC Applications

Zhiwei Xu, Deborah Winklea, Thomas C. Oh, Samuel Kim, Steven T.W. Chen, Yakov Royter, Maggy Lau, Irma Valles, Donald A. Hitko, James C. Li; HRL Laboratories, USA

**Abstract:** A programmable active band pass filter (BPF) has been designed in a chip-scale heterogeneous integration technology, which intimately integrates InP HBTs on a deep scaled CMOS technology. Therefore, the active BPF can leverage both high performance of InP HBT and high density and programmability of CMOS. The BPF prototype consists of a programmable gain amplifier (PGA), a 5th order BPF core, and a buffer. The BPF center frequency is programmable from 0.8 GHz to 2.4 GHz with 150 MHz pass band and delivers >55 dB out-of-band rejection. Four gain steps: 0, 6, 12, and 16 dB, are enabled by the front PGA to trade off noise and linearity performances. Due to the > 300 GHz fT of InP HBTs, the BPF core can leverage active-RC architecture for high linearity owing to the close-loop implementation. The prototype occupies  $1.5 \times 1.02$  mm<sup>2</sup> area together with pads and draws 106/121 mA from a 3.3 V power supply for 0.8/2.4 GHz bands respectively. In addition, the prototype demonstrates out-of-band OIP3s of 23.52/23.51 dBm for 0.8/2.4 GHz bands at the high gain mode.

# RM02A-2 10:30

#### A 6-b UWB Subsampling Track & Hold with 5.5-GHz ERBW in 40nm CMOS

Maarten Strackx<sup>1</sup>, Emiliano D'Agostino<sup>2</sup>, Paul Leroux<sup>1</sup>, Patrick Reynaert<sup>1</sup>; <sup>1</sup>Katholieke Universiteit Leuven, Belgium, <sup>2</sup>SCK • CEN, Belgium

**Abstract:** This paper presents an ultra wideband track and hold (T/H) circuit using direct RF subsampling for radar applications. The circuit enables digitization of the whole received UWB pulse instead of a sole distance measurement used in correlating receivers. In this way, more target information is acquired for further digital processing. Subsampling was applied to achieve a low power consumption of 1.4 mW which includes the T/H core and clock generator. The circuit operates on a rail-to-rail input using the bootstrapping technique. To avoid reliability issues caused by bootstrapping the sampling switch, bulk switching and precharge techniques are introduced. An effective resolution bandwidth of 5.5-GHz was measured with an accuracy of 6-b. The track and hold circuit has been implemented in 40 nm CMOS.

#### RMO2A-3 10:50 An 8-Bit 100-GS/s Distributed DAC in 28-nm CMOS

Hao Huang, Johannes Heilmeyer, Markus Grözing, Manfred Berroth; Universität Stuttgart, Germany **Abstract:** An 8-bit 100-GS/s digital-to-analog converter (DAC) using a distributed output topology in 28-nm low-power CMOS is presented. The ENOB and SFDR ranges from 5.3 bit and 41 dB to 3.2 bit and 27 dB from DC up to 24.9 GHz at 100 GS/s. The -3dB bandwidth is larger than 10 GHz. The 100 GS/s DAC is composed of two 50 GS/s time-interleaved sub-DACs and is operated from two 25 GHz clock signals with a phase shift of 90°. Due to this structure, the output frequency roll-off is comparable to a 50 GS/s DAC while the output frequency image rejection is comparable to a 100 GS/s DAC, easing the output frequency band utilization. With 1-kbyte on-chip memory the DAC can convert 1k symbols cyclically, which is sufficient for characterizing the DAC performance. The DAC consumes 2.5 W from a 1.1V/1.5V/2V power supply. The area of the test chip is 1.5mm<sup>2</sup>.

# Monday, 2 June 2014 10:10–11:50 Room TCC 13–14 Session RMO2B: K-Band Front-End ICs Chair: Danilo Manstretta, University of Pavia Co-Chair: Li Lin, Marvell Technology Group

# RM02B-1 10:10

#### A Compact 24–54GHz CMOS Band-Pass Distributed Amplifier for High Fractional Bandwidth Signal Amplification

V. Bhagavatula<sup>1</sup>, M. Taghivand<sup>2</sup>, Jacques C. Rudell<sup>1</sup>; <sup>1</sup>University of Washington, USA, <sup>2</sup>Qualcomm, USA

**Abstract:** This paper describes a compact 24–54 GHz two-stage band-pass distributed amplifier (BPDA) utilizing dual mirror-symmetric Norton transformations to reduce inductor component values allowing an area-efficient layout. The BPDA, implemented in a 40nm CMOS process, occupies an active area of 0.15mm<sup>2</sup>, has a 77% fractional-bandwidth, an overall gain of 7dB, a minimum inband IIP3 of 11dBm, in-band noise-figure less than 6.2dB while consuming 34mA from a 1V supply.

# RM02B-2 10:30

#### A K-Band 5-Bit Digital Linear Phase Rotator with Folded Transformer Based Ultra-Compact Quadrature Generation

Jong Seok Park, Hua Wang; Georgia Institute of Technology, USA

**Abstract:** This paper presents a K-band 5-bit vector modulator phase rotator. A fully differential based on a 6-port folded transformer I/Q generation passive network generates the quadrature signals at K-band with low loss, wide bandwidth and high precision, all within an ultra-compact foot-print; this makes the phase rotator design especially suitable for large-scaled high-density phased array systems. Two linear digital VGAs scale the quadrature signals to achieve the desired vector phase interpolation. As a proof-of-concept design, we implement the phase rotator in a SiGe BiCMOS process within a compact chip area of only 310  $\mu$ m by 380  $\mu$ m. It achieves -3 dB bandwidth of 6 GHz at the center frequency of 23.5 GHz. The maximum RMS phase error is only 2° for phase interpolation over the full 360° phase span. It consumes 4 mA from 2.5 V and the measured P<sub>1dB</sub> and IIP<sub>3</sub> are -16 dBm and -5.5 dBm, respectively. Leveraging the dense phase interpolation points to calibrate undesired I/Q mismatch is also demonstrated, which shows the robustness of the design.

## RM02B-3 10:50

#### K-Band FMCW Radar CMOS Front-End ICs with 13.3dBm Output Power

Gitae Pyo<sup>1</sup>, Jaemo Yang<sup>1</sup>, Hyunji Ku<sup>1</sup>, Choul-Young Kim<sup>2</sup>, Songcheol Hong<sup>1</sup>; <sup>1</sup>KAIST, Korea, <sup>2</sup>Chungnam National University, Korea

**Abstract:** This paper presents CMOS front-end ICs with 13.3 dBm output power for K-band FMCW radar, which is integrated in 0.13-µm CMOS technology. The transmitter consists of a voltage controlled oscillator, divider chain, power amplifier, and additional buffers. The receiver consists of a low-noise amplifier, IQ mixers, an IQ generator, and buffers. The leakage problem can be mitigated

by adopting differential topology and ground shielding. As a result, the receiver achieves a conversion gain of 35.7 dB, a P1dB of -31.6 dBm, and a DSB noise figure of 5.5 dB. The transmitter achieves the tuning range of  $23.8 \sim 24.5$  GHz and the phase noise of -104 dBc/Hz @ 1MHz offset. The receiver and transmitter chips consume 121.5 mW and 373.5 mW from a 1.5 V power supply, respectively. Using these two chips, the K-band FMCW radar module is implemented and verified by measuring the distance of an object.

# RM02B-4 11:10

#### A 10–50GHz True-Time-Delay Phase Shifter with Max 3.9% Delay Variation

Qian Ma, Domine M.W. Leenaerts, R. Mahmoudi; Technische Universiteit Eindhoven, The Netherlands

**Abstract:** A fully integrated passive True Time Delay (TTD) phase shifter with 32ps continuous changing delay time has been realized in a  $0.25\mu$ m SiGe:C BiCMOS technology. A new TTD architecture is proposed based on broadband matching technique, resulting in less than 4% delay variation over a very large, 10–50GHz frequency span, meanwhile maintaining an input return loss better than 10dB. The measured input 1dB compression point and input IP3 are +15.5dBm and +24.7dBm at 30GHz, respectively. The phase shifter core occupies less than 0.22mm<sup>2</sup>.

## Monday, 2 June 2014 10:10–11:50 Room TCC 15–16 Session RMO2C: Advanced PLL Techniques Chair: Danielle Griffith, Texas Instruments Co-Chair: Salvatore Levantino, Politecnico di Milano

# RM02C-110:10A 9.2–12.7GHz Wideband Fractional-N Subsampling PLL in 28nm CMOSwith 280fs RMS Jitter

Kuba Raczkowski, Nereo Markulic, Benjamin Hershberg, Joris Van Driessche, Jan Craninckx; imec, Belgium

**Abstract:** This paper describes a fractional-N subsampling PLL in 28nm CMOS. Fractional lock is achieved by using a 10bit digital-to-time converter (DTC) that generates a delayed sampling clock with minimal impact on PLL performance. Background calibration guarantees appropriate DTC gain, reducing spurs. The system achieves -38 dBc of integrated phase noise (280 fs RMS jitter) at 10 GHz when a worst-case fractional spur of -43 dBc is present. In-band phase noise is at the level of -104 dBc/Hz. The class-B VCO used can be tuned from 9.2 GHz to 12.7GHz (32%). The total power consumption of the synthesizer, including the VCO, is 13mW from 0.9V and 1.8V supplies.

# RM02C-2 10:30

# A 0.6/1.2-V 14.1-mW 96.8GHz-to-108.5GHz Transformer-Based PLL with Embedded Phase Shifter in 65-nm CMOS

Yue Chao<sup>1</sup>, Howard C. Luong<sup>1</sup>, Zhiliang Hong<sup>2</sup>; <sup>1</sup>HKUST, China, <sup>2</sup>Fudan University, China **Abstract:** A low-voltage and low-power 96.8–108.5GHz transformer-based PLL is implemented in a 65nm CMOS technology. Consuming only 14.1mW from 0.6V/1.2V supply, the PLL measures phase noise of -84dBc/Hz at 100-kHz offset and -88dBc/Hz at 1-MHz offset from a 99.4GHz carrier while occupying a core chip area of 0.39mm<sup>2</sup>. Moreover, with an embedded phase shifter, the PLL output phase can be shifted by 360° range with an average resolution of 3.9° and amplitude variation less than  $\pm$ 0.1dB.

# RM02C-3 10:50

# A Fractional-N DPLL with Adaptive Spur Cancellation and Calibration-Free Injection-Locked TDC in 65nm CMOS

Cheng-Ru Ho, Mike Shuo-Wei Chen; University of Southern California, USA

**Abstract:** A robust and low-cost fractional-N digital phase locked loop (DPLL) architecture is demonstrated via the proposed adaptive spur cancellation schemes and calibration-free time-to-digital converter (TDC). By leveraging the injection locked ring oscillator, the TDC achieves a fine resolution of  $\sim$ 7 ps that automatically tracks the period of digital controlled oscillator (DCO) and hence no TDC gain calibration is required over PVT. To suppress the spurious tones due to external or internal interferences, a gradient-based adaptive spur cancellation scheme is proposed and demonstrated more than 40dB improvement in the lab measurement. The proof-of-concept DPLL

prototype is implemented in 65nm CMOS and synthesizes frequencies between 2.7 to 4.8 GHz with fine frequency resolution of 610 Hz. The measured phase noise is -130dBc/Hz at 3MHz offset and the reference spur achieves -86.45 dBc.

# RM02C-4 11:10

# A 12GHz 67% Tuning Range 0.37pS $\text{RJ}_{\text{rms}}$ PLL with LC-VCO Temperature Compensation Scheme in 0.13 $\mu m$ CMOS

Yang You<sup>1</sup>, Deping Huang<sup>1</sup>, Jinghong Chen<sup>1</sup>, Sudipto Chakraborty<sup>2</sup>; <sup>1</sup>Southern Methodist University, USA, <sup>2</sup>Texas Instruments, USA

**Abstract:** This paper presents a PLL designed in 0.13 $\mu$ m CMOS for multi-data rate serial link applications. A novel temperature compensation scheme is proposed to reduce the LC-VCO temperature frequency drift without sacrificing the tuning range. Thus, the PLL covers a 5.6GHz to 13.4GHz tuning range by using just two VCO cores while remaining locked from -40°C to 85°C. At 25°C, the PLL has an RMS random jitter (RJ<sub>ms</sub>) of 0.37pS at 11.44GHz. The integrated jitter is less than 0.7pS over the tuning range and varies less than 50fS over temperature. The PLL consumes 50.88mW of power from a 1.2V supply at 12GHz and 25°C.

# RM02C-5 11:30

# A 60-GHz Sub-Sampling Frequency Synthesizer Using Sub-Harmonic Injection-Locked Quadrature Oscillators

Teerachot Siriburanon, Tomohiro Ueno, Kento Kimura, Satoshi Kondo, Wei Deng, Kenichi Okada, Akira Matsuzawa; Tokyo Institute of Technology, Japan

**Abstract:** This paper presents a 60-GHz sub-harmonic injection-locked quadrature frequency synthesizer with sub-sampling operation. This allows the proposed synthesizer to achieve relatively lower in-band phase noise through the use of sub-sampling operation, as well as good out-of-band phase noise through the use of sub-harmonic injection. The proposed synthesizer has been implemented in a standard 65nm CMOS technology. It can support all 60-GHz channels and achieves a phase noise of -115dBc/Hz at 10MHz offset. The sub-sampling operation helps reducing an integrated jitter from 12ps to 2.1ps. It consumes 20.2mW and 14mW from a 20GHz sub-sampling phase-locked loop (SS-PLL) and a quadrature injection-locked oscillator (QILO), respectively.

# Monday, 2 June 2014 10:10–11:50 Room TCC 18

#### Session RMO2D: Advancements in Distributive, Thermal, and Non-Linear Device Modeling

Chair: Francis M. Rotella, Peregrine Semiconductor Co-Chair: Francois Rivet, University of Bordeaux

# RM02D-1 10:10

Variable Delay Transmission Lines in Advanced CMOS SOI Technology

Shlomo Shlafman<sup>1</sup>, Benny Sheinman<sup>1</sup>, Danny Elad<sup>1</sup>, Alberto Valdes-Garcia<sup>2</sup>, Mihai A.T. Sanduleanu<sup>2</sup>; <sup>1</sup>IBM, Israel, <sup>2</sup>IBM, USA

**Abstract:** Variable (Delay) Transmission Lines (VTL) offer digital tuning of fabricated transmission lines to compensate for process variation in active and passive devices of RF silicon design enabling self-healing and post-production circuit tuning. A novel compact semi-analytic single ended VTL model, enabling accurate RFIC circuit level simulation to enhance design flow, was developed. VTL structures were fabricated and measured in IBM 32nm CMOS SOI technology. The 30,50,80 Ohm VTL structures, consisting of metal crossing lines between the signal line and ground plane that are connected to ground through CMOS switches, exhibit over 11%, 15%, 18% delay tuning range respectively with low insertion loss and good agreement between measured results and developed model simulations.

# RM02D-2 10:30

#### Analysis of Tunable Marchand Baluns

Luciano Boglione, Joel Goodman; Naval Research Laboratory, USA