# 2017 IEEE Radio Frequency Integrated Circuits Symposium

Honolulu, Hawaii, USA 4-6 June 2017

## **PROGRAM**

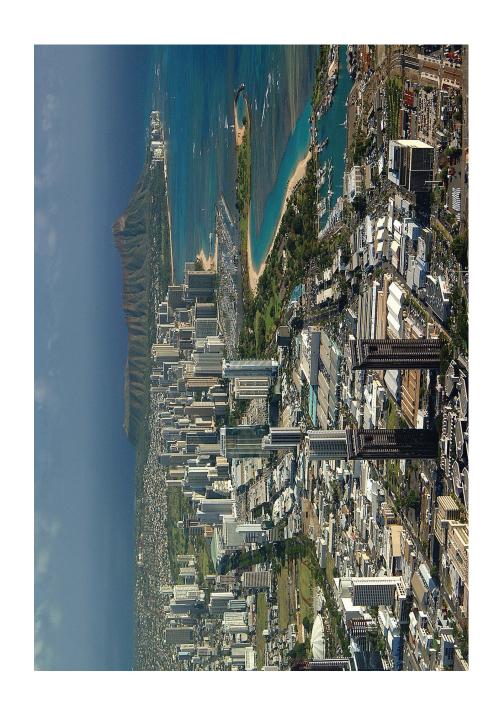

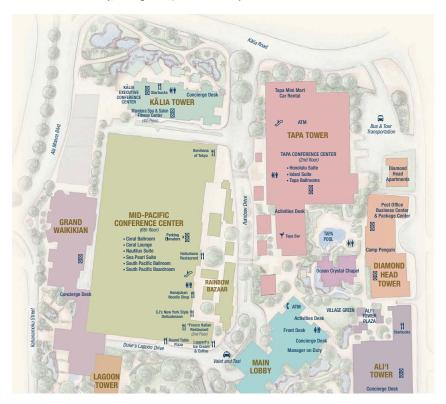

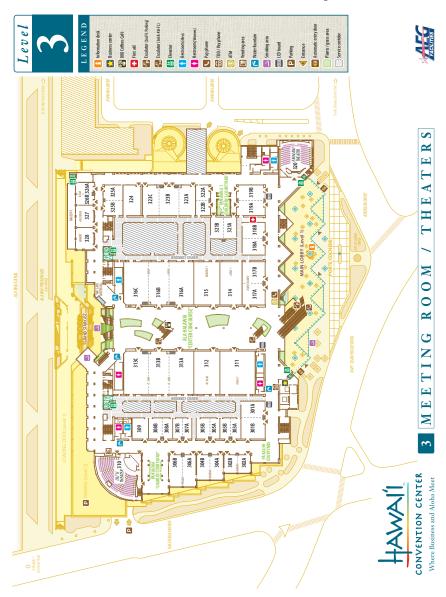

### Hawaii Convention Center and Hilton Hawaiian Village Waikiki Beach Resort

Sponsored by

IEEE Microwave Theory and Techniques Society

IEEE Electron Devices Society

and

IEEE Solid-State Circuits Society

#### RFIC Plenary, Reception, Joint Industry Showcase & Interactive Forum

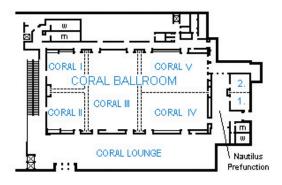

#### Sunday Evening, 4 June 2017 Hilton Hawaiian Village Waikiki Beach Resort Mid-Pacific Conference Center

After a busy day immersed in RFIC Workshops, enjoy a relaxing evening with your RFIC colleagues at these special Sunday night RFIC events, to be held in the Hilton Hawaiian Village Waikiki Beach Resort. Mid-Pacific Conference Center.

**18:00–19:30, Hilton, Mid-Pacific Conference Center, Coral Ballroom** — **The Plenary Session** kicks off the evening with the Student Paper Awards, RFIC Industry Best Paper Award, and RFIC Tina Quach Service Award ceremony followed by two outstanding 5<sup>th</sup> generation wireless plenary speakers, Dr. Seizo Onoe, CTO and EVP of NTT DOCOMO, INC., and Prof. Gabriel M. Rebeiz, Distinguished Professor at the University of California, San Diego.

19:30–21:30, Hilton, Mid-Pacific Conference Center, Coral Lounge — RFIC Welcoming Reception Featuring Joint Industry Showcase & Interactive Forum: Immediately following the Plenary Session is the RFIC Reception. Drinks and appetizers will be provided while you connect with old friends, make new acquaintances, and catch up on the latest developments in the wireless industry.

The Industry Showcase Session, held concurrently with the plenary reception, will highlight 10 selected papers submitted by authors from the industry. Jointly with the Industry Showcase, the Interactive Forum Session will present 15 papers in poster format. Authors of these papers will be present to discuss their innovative work, summarized in poster format, and some will also give a demonstration. The media will cover this event, making it an excellent opportunity to announce the latest RFIC developments and breakthroughs.

Admittance to all RFIC Sunday evening events is included with the RFIC Symposium registration and the Super-pass registration. Additionally, Sunday-night-only tickets can be purchased for those who cannot attend the rest of the RFIC Symposium but don't want to miss microwave week's opening event. Please see <a href="http://rfic-ieee.org/">http://rfic-ieee.org/</a> for more details.

The RFIC Reception is sponsored by the RFIC Steering Committee and through the generous support of our corporate sponsors:

# RFIC Symposium Schedule (4-6 June 2017)

| Event                                                  | Location                                                            | Sat 3 June  | Sun 4 June  | Mon 4 June                                               | Tue 6 June                 |

|--------------------------------------------------------|---------------------------------------------------------------------|-------------|-------------|----------------------------------------------------------|----------------------------|

| Registration                                           | HCC, Level 1, Main Lobby                                            | 08:00-19:00 | -00:00      | 07:00–19:00                                              | 07:00–18:00                |

| Workshop Speakers' Breakfast                           | HCC, Level 3, Rooms 323 A–C                                         |             | -00:00      | 07:00-08:00                                              |                            |

| Workshops & Short Courses                              | HCC, Level 3, Rooms 312–325                                         |             | -00:80      | 08:00-17:00                                              |                            |

| Workshop Lunch                                         | HCC, Level 3, Ala Halawai<br>Center Concourse                       |             | 12:00-      | 12:00–13:00                                              |                            |

| Plenary Session                                        | Hilton, Mid-Pacific Conference<br>Center, Coral Ballroom            |             | 18:00–19:30 |                                                          |                            |

| Reception, Joint Industry Showcase & Interactive Forum | y Showcase & Hilton, Mid-Pacific Conference<br>Center, Coral Lounge |             | 19:30–21:30 |                                                          |                            |

| Speakers' Breakfast                                    | HCC, Level 3, Rooms 323 A–C                                         |             |             | 07:00-08:00                                              | -08:00                     |

| Technical Sessions                                     | HCC, Level 3, Rooms 312–313B                                        |             |             | 08:00-09:40<br>10:00-11:40<br>13:30-15:10<br>15:30-17:10 | 08:00-09:40<br>10:00-11:40 |

| Panel Sessions                                         | HCC, Level 3, Rooms 316C                                            |             |             | 11:45–12:45                                              | -12:45                     |

|                                                        |                                                                     |             |             |                                                          |                            |

#### **TABLE OF CONTENTS**

The RFIC Symposium is the premier IC conference focused exclusively on the latest developments in RF, Microwave, and Millimeter-Wave Integrated Circuit technology and innovation from both industry and academia.

|        | Table of Contents                                                                        | 1        |

|--------|------------------------------------------------------------------------------------------|----------|

|        | Welcome Message from Chairs                                                              | 2        |

|        | Steering Committee                                                                       | 4        |

|        | Executive Committee                                                                      | 4        |

|        | Advisory Board                                                                           | 4        |

|        | Technical Program Committee                                                              | 5        |

|        | RFIC 2017 Schedule                                                                       | 6        |

|        | Schedule: Plenary, Reception, Joint Industry Showcase & Interactive Forum                | 7        |

|        | Best Student Paper Award Finalists                                                       | 8        |

|        | Plenary Speakers                                                                         | . 10     |

|        | Industry Showcase                                                                        | . 12     |

|        | RSUIF: Interactive Forum                                                                 | 14       |

|        | RMO1A: 28GHz Phased-Array Transceivers for 5G Systems                                    | 20       |

| MONDAY | RMO1B: Advanced Technologies for Optical, Millimeter-Wave and Radio Frequency Apps       |          |

|        | RMO1D: High-Performance Frequency Synthesizers                                           |          |

|        | RMO2A: Radio Building Blocks for 5G Systems                                              |          |

|        | RMO2B: Modeling & Characterization for Emerging High Frequency & RF Front-End Apps       | 28       |

|        | RMO2D: Millimeter-Wave and THz Sources                                                   |          |

|        | RMO3A: Ultra-Low Power Wake-Up Receivers                                                 |          |

|        | RM03B: Next Generation Transmitters and Receivers for Cellular and Wireless Connectivity | 34       |

|        | RM03D: X Band PAs and Beyond.                                                            |          |

|        | RMO4A: Low-Power Transceivers                                                            |          |

|        | RM04B: RF Circuits for Emerging Applications and Gigabit Optical Links                   | 40       |

|        | RMO4D: Reconfigurable Receiver Front-Ends                                                |          |

|        | RTU1A: RF Front-End Building Blocks                                                      |          |

| JESDA  | RTU1A: AF Front-End Building Blocks                                                      | . 44     |

|        | RTU1D: Reconfigurable Multi-Mode PAs                                                     | .40      |

|        | DTUO A. F. II Denday Interference Decilient and Hammonia Delection Decisions             |          |

|        | RTU2A: Full-Duplex, Interference-Resilient and Harmonic-Rejection Receivers              | 50<br>50 |

|        | RTU2B: System-on-Chip for Millimeter-Wave and Above                                      | 54<br>74 |

|        | RTU2D: Power Amplifiers in Advanced Technologies                                         |          |

|        | Panel Sessions                                                                           |          |

|        | Workshops and Short Courses                                                              |          |

|        | Registration                                                                             |          |

|        | On-Site Registration                                                                     | -        |

|        | Registration Rates                                                                       | -        |

|        | Visa Information                                                                         | -        |

|        | Social/Networking Events                                                                 |          |

|        | Conference Venue Maps                                                                    | . 98     |

#### **Welcome Message from Chairs**

We invite you to participate in the 2017 IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, to be held in Honolulu, Hawaii, on 4-6 June 2017. RFIC Symposium is the premier IC design conference focused exclusively on the latest advances in RF, Microwave and Millimeter-Wave integrated circuit (IC) technologies and designs, as well as innovations in high frequency analog/mixed-signal ICs. We cordially invite you to participate in this global event!

The RFIC Symposium is an annual IEEE conference that is combined with the International Microwave Symposium (IMS), ARFTG and the Industry Exhibition to form "Microwave Week", the largest worldwide RF/microwave technical meeting of the year. Microwave week will be held at the Hawaiian Convention Center in Honolulu Hawaii which is in close proximity to nearby Waikiki. Attendees will have the opportunity to interact with world experts, expand their network, and leave invigorated with new ideas and a drive to innovate.

RFIC 2017 will continue to offer a number of initiatives: the 2-page industry brief format, allowing the latest state-of-the-art RF IC design results to be presented without requiring die photos and detailed schematics, will continue in 2017. The popular Industry Showcase Session, featuring poster presentations (and optional demos) of the most innovative and highly-rated industrial papers (both two and four page formats), will be the highlight during the RFIC Reception in the evening of Sunday, 4 June 2017. Again this year, the Industry Showcase will be held jointly with the Interactive Forum (IF) Session during the RFIC Reception, which will offer the attendees an enhanced interactive experience in a relaxed environment. To improve academic submissions, all of the RFIC student paper finalists will receive complimentary RFIC registration. Students may volunteer to help with RFIC (and/or IMS) conference logistics in exchange for complimentary conference registration, meals, T-shirts, and other benefits. The joint RFIC/IMS PhD Student Sponsorship Initiative Program will continue to involve selected first and second-year PhD students to complete technical assignments during the conference in exchange for complimentary conference registrations, lodging and meals.

RFIC 2017 will open on Sunday, 4 June 2017, with 16 workshops (10 full-day and 6 half-day). These workshops cover a wide range of topics including: "5G mm-Wave IC Front-End Co-Design with Antenna, Packaging, and Testing for Future SOC Solutions", "Advanced Concepts and Architectures for Future RF and mm-Wave Transceivers in Nanoscale CMOS", "CMOSpace: Challenges and Accomplishments of Designing Advanced CMOS SoC for Space Communication and Instrumentation", "Efficiency Enhancement Techniques for Linear and High Bandwidth Power Amplifiers", "Energy-Efficient RF Transceiver IC and System Design for Healthcare Applications", "Frequency Synthesis and Clock Distribution for Massive MIMO and Phased-Arrays in 5G Communication Systems and Beyond", "High Performance Power Efficient Clock Generation for Internet of Things Applications", "Highly Digital CMOS Transmitters with Embedded Power Amplifiers", "Microwave through Sub-THz Imaging and Sensor Array Technology for Security, Industrial, Commercial and Medical Applications", "Millimeter Wave for 5G: Which Systems with Which Frequency Band — 5G RF Transceiver Design and System Aspects', "Polar, ET, Out-Phasing, Doherty, Pre-Distortion: Which One Survives at mm-Wave Frequencies?", "RFIC Design Challenges for the IoT at Scale", "RFIC Design for Automotive Radar", "RFIC Design in CMOS FinFET and FD-SOI", "RF-Inspired Silicon Photonic", "The Many Flavors of CMOS/Bipolar RF Harmonic Oscillators". These workshops cover some of the hottest topics in RFIC design.

The RFIC Plenary Session will be held in the evening beginning with the conference highlights, the presentation of the Student Paper Awards and the Industry Best Paper Award. The plenary session will conclude with focused talks on "5G" beginning with Dr. Seizo Onoe, CTO and EVP of NTT Docomo who will enlighten us on the "Deployment Realities of 5G". The second talk will be given by the Wireless Communications Industry Chair Professor at UCSD and National Academy of Engineering member, Prof. Gabriel Rebeiz, who will share his vision on "RFIC/Silicon-Based Phased Arrays and Transceivers for 5G".

Immediately following the plenary session will be the RFIC 'interactive' Sunday reception that will highlight our industry show-case and interactive forum papers in an engaging social and technical evening event supported by the RFIC Symposium corporate sponsors. You will not want to miss the RFIC Reception this year!

On Monday and Tuesday, the RFIC will have multiple tracks of oral technical paper sessions. Two entertaining panels will be featured during lunchtime on both days. The Monday panel session is titled "5th Generation Wireless — Where is That Going and What's in It for Me?" while the Tuesday panel session will be a gameshow-quiz titled "Who Wants to be a Millimeterwavionaire?". Make sure to bring your opinions and questions and come prepared to answer technical trivia at the Tuesday panel to win prizes. The afternoon 5G summit technical talks will provide high level 5G technology overview that will complement the 5G-focused RFIC morning technical sessions. A separate registration will be required for the 5G summit.

On behalf of the RFIC steering and executive committees, we welcome you to join us at the 2017 RFIC Symposium in Honolulu Hawaii! Please visit the RFIC 2017 website (<a href="http://rfic-ieee.org">http://rfic-ieee.org</a>) for more details and updates.

**Kevin W. Kobayashi** General Chair Oorvo

Stefano Pellerano TPC Co-Chair Intel

**Walid Ali-Ahmad** TPC Chair Qualcomm

#### **Steering Committee**

Kevin W. Kobayashi, Qorvo, General Chair Walid Ali-Ahmad, Qualcomm, TPC Chair Stefano Pellerano, Intel, TPC Co-Chair Srenik Mehta, Google, Publications Chair & Digest Chair Andre Hanke, Intel, RFIC Program Book Chair Ranjit Gharpurey, University of Texas at Austin, IMS Program Book Chair Salvatore Levantino, Politecnico di Milano, Session Organization Chair Danilo Manstretta, University of Pavia, *Transactions Chair – ISSC* Donald Y.C. Lie, Texas Tech University, *Transactions Chair – TMTT* Nick Cheng, Skyworks Solutions, *Publicity Chair* Oren Eliezer, PHAZR. Panel Sessions Chair Domine Leenaerts, NXP Semiconductors, Workshop Chair Osama Shana'a, MediaTek, Workshop Co-Chair Li Lin, Consultant, Student Papers Chair Yuhua Cheng, Peking University, Asia Pacific Liaison Freek van Straten, Ampleon, European Liaison Brian Floyd, North Carolina State University, Industry Liaison Waleed Khalil, Ohio State University, Secretary & IF Sessions Steven Turner, BAE Systems, Paper Submission Website Amanda Scacchitti, Publicity & Advisor Elsie Vega, IEEE, Conference Manager Robert Alongi, IEEE, Finances Zaher Bardai, IMN Epiphany, VISAs Michael Oakley, Raytheon, Website Chair Sandy Owens, MPA, Submissions Software

#### **Executive Committee**

Bertan Bakkaloglu, *Arizona State University*Jacques C. Rudell, *University of Washington*Lawrence Kushner, *BAE Systems*Albert Wang, *University of California, Riverside*Kevin W. Kobayashi, *Qorvo*

#### **Advisory Board**

Jenshan Lin, *University of Florida*Stefan Heinen, *RWTH Aachen University*Joseph Staudinger, *NXP Semiconductors*Luciano Boglione, *Naval Research Laboratory*Natalino Camilleri, *Nitero*Yann Deval, *University of Bordeaux*David Ngo, *Qorvo*

#### **Technical Program Committee**

Ali Afsahi, Broadcom Ehsan Afshari, University of Michigan Pietro Andreani, Lund University Amin Arbabian, Stanford University Himanshu Arora, Cirrus Logic Edmund Balboni, Analog Devices Jean-Baptiste Begueret, University of Bordeaux Pierre Busson, STMicroelectronics Richard Chan, Qorvo Nick Cheng, Skyworks Solutions Yuhua Cheng, Peking University Yuan-Hung Chung, MediaTek Oren Eliezer. PHAZR Kamran Entesari, Texas A&M University Ayman Fayed, Obio State University Brian Floyd, North Carolina State University Eric Fogleman, MaxLinear Xiang Gao, Marvell Semiconductor Ranjit Gharpurey, University of Texas at Austin Vito Giannini, Uhnder Jane Gu, University of California, Davis Ping Gui, Southern Methodist University Andre Hanke. Intel Ramesh Harjani, University of Minnesota Hossein Hashemi, University of Southern California Gary Hau, Qualcomm Hiva Hedayati, Applied Micro Circuits Mona Hella, Rensselaer Polytechnic Institute Gernot Hueber, NXP Semiconductors Vipul Jain, Anokiwave Waleed Khalil, Obio State University Jaber Khoja, Rockwell Collins Jennifer Kitchen, Arizona State University Eric Klumperink, University of Twente Harish Krishnaswamy, Columbia University

Timothy LaRocca, Northrop Grumman Fred Lee, Verily Life Sciences Tzung-Yin Lee, Skyworks Solutions Domine Leenaerts. NXP Semiconductors Salvatore Levantino, Politecnico di Milano Donald Y.C. Lie, Texas Tech University Li Lin, Consultant Yao-Hong Liu, imec Danilo Manstretta, University of Pavia Srenik Mehta, Google Mohyee Mikhemar, Broadcom Arun Natarajan, Oregon State University Jeyanandh Paramesh, Carnegie Mellon University Edward Preisler, TowerJazz Raja Pullela, *MaxLinear* Patrick Reynaert, KU Leuven Francois Rivet, University of Bordeaux Bodhisatwa Sadhu, IBM T.J. Watson Research Center Osama Shana'a, MediaTek Margaret Szymanowski, NXP Semiconductors Julian Tham, Cypress Semiconductor Leon van den Oever, Radio Semiconductor Freek van Straten, Ambleon Jeffrey Walling, University of Utah Hua Wang, Georgia Institute of Technology Yanjie Wang, Intel David Wentzloff, University of Michigan Magnus Wiklund, Qualcomm James Wilson, US Army Research Laboratory Renaldi Winoto. Marvell Semiconductor Haolu Xie. ZTE Hongtao Xu, Fudan University Li-Wu Yang, RF Integrated Gary Zhang, Guangdong University of Technology Yuxiang Zheng, Huawei Technologies

#### **RFIC 2017 Schedule**

#### Saturday, 3 June 2017

08:00–19:00 Registration — Hawaii Convention Center (HCC), Level 1, Main Lobby

#### Sunday, 4 June 2017

- 07:00–19:00 Registration HCC, Level 1, Main Lobby

- 07:00–08:00 Workshop Speakers' Breakfast HCC, Level 3, Rooms 323 A-C

- 08:00–17:00 Workshops and Short Courses, HCC, Level 3, Rooms 312–325

- 12:00–13:00 Workshops Lunch HCC, Level 3, Ala Halawai Center Concourse

- 18:00–19:30 RFIC Plenary Hilton Hawaiian Village Waikiki Beach Resort (Hilton), Mid-Pacific Conference Center, Coral Ballroom

- 19:30—21:30 RFIC Welcoming Reception Featuring Joint Industry Showcase & Interactive Forum

Hilton, Mid-Pacific Conference Center, Coral Lounge

#### Monday, 5 June 2017

- 07:00–19:00 Registration HCC, Level 1, Main Lobby

- 07:00-08:00 Speakers' Breakfast HCC, Level 3, Rooms 323 A-C

- 07:00–08:00 Workshop Speakers' Breakfast HCC, Level 3, Rooms 323 A–C

- 08:00–17:00 Workshops and Short Courses, HCC, Level 3, Rooms 312–325

- 08:00–09:40 RM01A HCC, Room 312: 28GHz Phased-Array Transceivers for 5G systems

RM01B HCC, Room 313A: Advanced Technologies for Optical, Millimeter-Wave

and Radio Frequency Applications

- RMO1D HCĈ, Room 313B: High-Performance Frequency Synthesizers

- 09:40–10:00 Break HCC, Level 3, Ala Halawai Center Concourse

- 10:00–11:20 RMO2A HCC, Room 312: Radio Building Blocks for 5G Systems

- 10:00–11:40 RMO2B HCC, Room 313A: Modeling and Characterization for Emerging High Frequency and RF Front-End Applications RMO2D — HCC, Room 313B: Millimeter-Wave and THz Sources

- 11:45–12:45 RFIC Panel Session HCC, Room 313C

- 12:00–13:00 Workshops Lunch HCC, Level 3, Ala Halawai Center Concourse

- 13:30–15:10 RM03A HCC, Room 312: Ultra-Low Power Wake-Up Receivers RM03B HCC, Room 313A: Next Generation Transmitters and Receivers for Cellular and Wireless Connectivity RM03D HCC, Room 313B: X Band PAs and Beyond

- 15:10–15:30 Break HCC, Level 3, Ala Halawai Center Concourse

- 15:30–17:05 RMO4A HCC, Room 312: Low-Power Transceivers

- RMO4B HCC, Room 313A: RF Circuits for Emerging Applications and Gigabit Optical Links

- RMO4D HCC, Room 313B: Reconfigurable Receiver Front-Ends

#### Tuesday, 6 June 2017

- 07:00–18:00 Registration HCC, Level 1, Main Lobby

- 07:00–08:00 Speakers' Breakfast HCC, Level 3, Rooms 323 A–C

- 08:00–09:40 RTU1A HCC, Room 312: RF Front-End Building Blocks

RTU1B HCC, Room 313A: Advanced Millimeter-Wave Circuit Techniques

RTU1D HCC, Room 313B: Reconfigurable Multi-Mode PAs

- 09:40–10:00 Break HCC, Level 1, Exhibit Hall II

- 10:00–11:40 RTU2A HCC, Room 312: Full-Duplex, Interference-Resilient and Harmonic-Rejection Receivers

RTU2B HCC, Room 313A: System-on-Chip for Millimeter-Wave and Above

- RTU2D HCC, Room 313B: Power Amplifiers in Advanced Technologies

- 11:45–12:45 RFIC Panel Session HCC, Level 3, Room 316C

## Schedule: Plenary, Reception, Joint Industry Showcase & Interactive Forum

#### Sunday Evening, 4 June 2017 Hilton Hawaiian Village Waikiki Beach Resort

## 18:00-19:30 **RFIC Plenary**

#### **Mid-Pacific Conference Center, Coral Ballroom**

Chair: Kevin W. Kobayashi, Qorvo Co-Chair: Walid Ali-Ahmad, Qualcomm Co-Chair: Stefano Pellerano, Intel

| 18:00 | Welcome Message from General Chair and TPC Chairs,                        |

|-------|---------------------------------------------------------------------------|

|       | Student Paper Awards, Industry Best Paper Award, Tina Quach Service Award |

| 18:30 | Deployment Realities of 5G                                                |

|       | Seizo Onoe, NTT DOCOMO                                                    |

| 19:00 | RFIC/Silicon-based Phased Arrays and Transceivers for 5G                  |

|       | Gabriel M. Rebeiz, University of California, San Diego                    |

# 19:30–21:30 RFIC Welcoming Reception Featuring Joint Industry Showcase & Interactive Forum Mid-Pacific Conference Center, Coral Lounge

The RFIC "Interactive" Reception starts immediately after the Plenary Session and will highlight 10 industry show-case and 15 interactive forum papers in an engaging social and technical evening event with food and drinks. This event is supported by the RFIC Symposium corporate sponsors. You will not want to miss the RFIC Reception this year! Authors of these showcase and interactive forum papers will present their innovative work, summarized in poster format. Some industry showcase papers will also have demonstrations. The press will cover this event giving the attendees an excellent opportunity to hear the latest RFIC developments and breakthroughs in person. After the reception, you will be able to enjoy the numerous shops in the Hawaiian Village and an evening stroll along Waikiki beach.

#### **Best Student Paper Award Finalists**

One of the missions of RFIC Symposium is to promote academic research and education. As part of the Best Student Paper Award program, several finalists are nominated every year by RFIC Technical Program Committee to enter the final contest where the top-three best papers are selected. All finalists benefit from a complimentary RFIC registration. The top-three Best Student Papers will be announced during the RFIC Plenary Session on 4 June 2017 in Honolulu. Each winner will receive an honorarium and a plaque. This year's Best Student Paper Award finalists are:

Validation of a Functional Principle for a Broadband Millimeter-Wave Power Detection

Structure in a Recent BiCMOS Technology

F. Trenz<sup>1</sup>, R. Weigel<sup>1</sup>, Dietmar Kissinger<sup>2</sup>

<sup>1</sup>FAU Erlangen-Nürnberg, Germany, <sup>2</sup>IHP, Germany

RMO1B-4 09:00

A Low-Noise Inductor-Less Fractional-N Sub-Sampling PLL with Multi-Ring Oscillator

Dongyi Liao, Ruixin Wang, Fa Foster Dai

Auburn University, USA

RMO1D-5 09:20

A 29-to-57GHz AM-PM Compensated Class-AB Power Amplifier for 5G Phased Arrays in 0.9V 28nm Bulk CMOS

Marco Vigilante, Patrick Reynaert

Katholieke Universiteit Leuven, Belgium

RMO2A-2 10:20

Accurate Modelling and Optimization of Inhomogeneous Substrate Related Losses in SPDT

Switch IC Design for WLAN Applications

Fadoua Gacim, Philippe Descamps

CRISMAT. France

RMO2B-1 10:00

An Ultra-Wideband Harmonic Radiator with a Tuning Range of 62GHz (28.3%) at 220GHz

Ali Mostajeran, Ehsan Afshari

Cornell University, USA

RMO2D-5 11:20

A 335µW -72dBm Receiver for FSK Back-Channel Embedded in 5.8GHz Wi-Fi OFDM Packets

Jaeho Im, Hun-Seok Kim, David D. Wentzloff

University of Michigan, USA

RMO3A-3 14:10

A Wideband Linear Direct Digital RF Modulator Using Harmonic Rejection and I/Q-

Interleaving RF DACs

M. Mehrpoo, Mohsen Hashemi, Yiyu Shen, Rene van Leuken, Morteza S. Alavi,

Leo C.N. de Vreede

Technische Universiteit Delft, The Netherlands

RMO3B-1 13:30

Sunday, 4 June 2017

18:00-18:30

Hilton Coral Ballroom

SiGe BiCMOS Linear Modulator Drivers with 4.8- $V_{pp}$  Differential Output Swing for 120-GBaud Applications

Robert J.A. Baker<sup>1</sup>, James Hoffman<sup>1</sup>, Peter Schvan<sup>2</sup>, Sorin P. Voinigescu<sup>1</sup>

<sup>1</sup>University of Toronto, Canada, <sup>2</sup>Ciena, Canada

RMO4B-4 16:30

85-110GHz CMOS Tunable Nonreciprocal Transmission Line with 45dB Isolation for

Wideband Transceivers

Chang Yang, Ping Gui

Southern Methodist University, USA

RMO4D-5 16:50

A Wideband Receiver Employing PWM-Based Harmonic Rejection Downconversion

Heechai Kang, Wei-Gi Ho, Vineet Singh, Ranjit Gharpurey

University of Texas at Austin, USA

RTU2A-5 11:20

Fully-Scalable 2D THz Radiating Array: A 42-Element Source in 130-nm SiGe with 80-µW Total Radiated Power at 1.01THz

Zhi Hu, Ruonan Han

MIT, USA

RTU2B-2 10:20

<u>Student Paper Contest Eligibility</u>: The student must have been a full time student (9 hours/term graduate, 12 hours/term undergraduate) during the time the work was performed. The student must be the lead author of the paper and must present the paper at the Symposium. A memorandum will be automatically sent to the advisor to certify that the work was done by the student.

<u>Judging Procedure</u>: Student papers are reviewed and admitted to the conference in the same manner as all other conference papers. After the paper review process is completed, each technical program subcommittee recommends a maximum of two student papers as finalists. A student paper contest committee consisting of one representative from each subcommittee is then formed to review all the finalists and select the top three papers. Papers accepted for the competition are judged on content.

Li Lin Student Programs Chair Consultant

#### **Plenary Speaker 1**

#### Seizo Onoe Chief Technology Officer and Executive Vice President. NTT DOCOMO

#### **Deployment Realities of 5G**

**Abstract:** 5G is stimulating our imagination and expectations for a new world that it may bring about by the year 2020.5G is aimed at meeting a wide range of requirements such as further enhanced mobile broadband, massive connections and extremely long battery life for IoT, and reliable critical communications with low latency. Furthermore, it is highly expected to invent new business models and ecosystems across the industries. 5G discussion is gathering momentum and so heated that it is becoming a sort of boom, which is sometimes generating unintended misconceptions and myths. Today we as the whole industry are making various strong efforts for 5G, including accelerated standardization activities toward its early realization, forming of alliances, and experimental trials. In the talk, 5G technologies, schedule, lessons learnt from the past generations, and experimental trials and their results are discussed. The observed 5G myths are also described.

#### **About Seizo Onoe**

Seizo Onoe was named Chief Technology Officer and Executive Vice President and a Member of the Board of Directors in June 2012. Mr. Onoe became a Senior Vice President and General Manager of the R&D Strategy Department in June 2008. He was a Vice President and took positions as General Manager of the Radio Access Network related development departments from July 2002 to June 2008. He has been responsible for leading initiatives in the research and development of the analog cellular system, the digital cellular system, W-CDMA/ HSPA, LTE, LTE-Advanced and 5G. He is working on the research and development of radio access networks, core networks, consumer devices and cloud services. He has worked for NTT and NTT DOCOMO since 1982, acquiring more than 30 years of experience. Mr. Onoe has a master's degree in electronics from the Kyoto University Graduate School of Engineering.

#### **Plenary Speaker 2**

Gabriel M. Rebeiz Distinguished Professor, University of California, San Diego

## RFIC/Silicon-Based Phased Arrays and Transceivers for 5G

**Abstract:** The 5G standard promises a revolution in wireless data transfer with Gbps links over kilometers at millimeter-wave frequencies. This is possible using high-gain antenna arrays resulting in "directive communications" between the base-station and the user, either in a phased-array or in a MIMO configuration. A key challenge is the construction of low-cost phased-arrays and wideband transceivers at 20–60 GHz. Prof. Rebeiz will present the progression of phased-array systems from defense-oriented applications to becoming the cornerstone of commercial 5G systems, and the role of silicon RFICs and advanced packaging to making this happen.

#### About Gabriel M. Rebeiz

Gabriel M. Rebeiz is one of the fathers of silicon RFIC phased-arrays. Starting in 2001 with his work at Boeing and MACOM, Prof. Rebeiz has taken this technology from its infancy to fully-deployed SATCOM phased-arrays, 60 GHz base-station phased-arrays, automotive radar phased-arrays, and now, 28 GHz 5G systems operating. He holds a Ph.D. in electrical engineering from the California Institute of Technology (Caltech), and is currently the Wireless Communications Industry Endowed Chair Professor at UCSD. He has graduated 85 Ph.D. students and post-docs, has more than 650 IEEE publications, and has received the Microwave Prize twice, both on phased-array topics. In 2016, Prof. Rebeiz was elected to the National Academy of Engineering for his contribution to low-cost phased arrays.

#### **Industry Showcase**

#### Chair: Brian Floyd, North Carolina State University

The Industry Showcase Session, held concurrently with the plenary reception and the Interactive Forum, will highlight 10 selected papers submitted by authors from industry. Authors of these papers will be present to discuss their innovative work, summarized in poster format, and some will also show a demonstration. The media will cover this event, making it an excellent opportunity to announce the latest RFIC developments and breakthroughs. The Best Industry Paper Award will be awarded to the author of one selected paper among these. This year's Industry Showcase papers are listed below.

A 28GHz CMOS Direct Conversion Transceiver with Packaged Antenna Arrays for 5G Cellular System

LG Electronics, Korea

$Hong-Teuk\ Kim,\ Byoung-Sun\ Park,\ Seung-Min\ Oh,\ Seong-Sik\ Song,\ Jong-Moon\ Kim,\ So-Hyeong\ Kim,\ Tak-Su\ Moon,\ Seung-Yeon\ Kim,\ Ji-Young\ Chang,\ Sung-Woong\ Kim,\ Woo-Seong\ Kang,\ Seung-Yoon\ Jung,\ Geum-Young\ Tak,$

Jin-Kyoung Du, Yu-Suhk Suh, Yo-Chuol Ho

RMO1A-3 08:40

A 73GHz PA for 5G Phased Arrays in 14nm FinFET CMOS

Intel. USA

Steven Callender, Stefano Pellerano, Christopher Hull

RTU2D-5 11:20

A Fully Integrated 75–83GHz FMCW Synthesizer for Automotive Radar Applications with -97dBc/Hz Phase Noise at 1MHz Offset and 100GHz/mSec Maximal Chirp Rate ON Semiconductor, Israel

Jakob Vovnoboy, Run Levinger, Nadav Mazor, Danny Elad

RMO1D-2 08:20

A~200μm  $\times~200$ μm  $\times~100$ μm, 63nW, 2.4GHz Injectable Fully-Monolithic Wireless Bio-Sensing System

<sup>1</sup>Verily, USA, <sup>2</sup>Google, USA, <sup>3</sup>Cobalt Robotics, USA

$S.\ O'Driscoll^1, S.\ Korhummel^1, P.\ Cong^1, Y.\ Zou^1, K.\ Sankaragomathi^1, J.\ Zhu^2, T.\ Deyle^3, A.\ Dastgheib^1, B.\ Lu^1, Lu^2, Lu^2,$

M. Tierney<sup>1</sup>, J. Shao<sup>1</sup>, C. Gutierrez<sup>1</sup>, S. Jones<sup>1</sup>, H. Yao<sup>1</sup>

RMO4B-3 16:10

95μW 802.11g/n Compliant Fully-Integrated Wake-Up Receiver with -72dBm Sensitivity in 14nm FinFET CMOS

<sup>1</sup>Intel, USA, <sup>2</sup>Carnegie Mellon University, USA

Erkan Alpman<sup>1</sup>, Ahmad Khairi<sup>2</sup>, Minyoung Park<sup>1</sup>, V. Srinivasa Somayazulu<sup>1</sup>, Jeffrey R. Foerster<sup>1</sup>, Ashoke Ravi<sup>1</sup>,

Stefano Pellerano<sup>1</sup>

RMO3A-2 13:50

A 4mW-RX 7mW-TX IEEE 802.11ab Fully-Integrated RF Transceiver

Holst Centre, The Netherlands

Ao Ba, Kia Salimi, Paul Mateman, Pepijn Boer, Johan van den Heuvel, Jordy Gloudemans, Johan Dijkhuis, Ming Ding, Yao-Hong Liu, Christian Bachmann, Guido Dolmans, Kathleen Philips

RMO4A-2 15:50

Sunday, 4 June 2017

19:30-21:30

**Hilton Coral Lounge**

## A Wideband SiGe BiCMOS Transceiver Chip-Set for High-Performance Microwave Links in the 5.6–43.5GHz Range

<sup>1</sup>Nokia Bell Labs, USA, <sup>2</sup>Nokia, France

Y. Baeyens<sup>1</sup>, S. Shahramian<sup>1</sup>, B. Jalali<sup>1</sup>, P. Roux<sup>1</sup>, J. Weiner<sup>1</sup>, A. Singh<sup>1</sup>, M. Moretto<sup>2</sup>, P. Boutet<sup>2</sup>, P. Lopez<sup>2</sup> RTU2B-3 10:40

## A 12-b, 1-GS/s 6.1mW Current-Steering DAC in 14nm FinFET with 80dB SFDR for 2G/3G/4G Cellular Application

Samsung, Korea

Jaekwon Kim, Woojin Jang, Yanghun Lee, Seunghyun Oh, Jongwoo Lee, Thomas Byunghak Cho RMO4R-1 15:30

#### RF-pFET in Fully Depleted SOI Demonstrates 420GHz $F_{\scriptscriptstyle T}$

<sup>1</sup>GLOBALFÓUNDRIES, USA, <sup>2</sup>GLOBALFOUNDRIES, Singapore, <sup>3</sup>GLOBALFOUNDRIES, Germany, <sup>4</sup>CEA-LETI, France

Josef Watts<sup>1</sup>, Kumaran Sundaram<sup>2</sup>, Kok Wai Johnny Chew<sup>2</sup>, Steffen Lehmann<sup>3</sup>, Shih Ni Ong<sup>2</sup>, Wai Heng Chow<sup>2</sup>, Lye Hock Chan<sup>2</sup>, Jerome Mazurier<sup>4</sup>, Christoph Schwan<sup>3</sup>, Yogadissen Andee<sup>4</sup>, Thomas Feudel<sup>3</sup>, Luca Pirro<sup>4</sup>, Elke Erben<sup>3</sup>, Edward Nowak<sup>1</sup>, Elliot Smith<sup>3</sup>, El Mehdi Bazizi<sup>3</sup>, Thorsten Kammler<sup>3</sup>, Richard Taylor III<sup>1</sup>, Bryan Rice<sup>3</sup>, David Harame<sup>3</sup> RMO1B-3 08:40

## A Precision 140MHz Relaxation Oscillator in 40nm CMOS with 28ppm/°C Frequency Stability for Automotive SoC Applications

Infineon Technologies, Austria

Dmytro Cherniak, Roberto Nonis, Fabio Padovan

RSUIF-15 19:30

#### Sunday 4th June 2017 19:30-21:30

#### Hilton Coral Lounge Session RSUIF: Interactive Forum

Chair: Waleed Khalil, Ohio State University

Co-Chair: Jennifer Kitchen, Arizona State University

#### RSUIF-1 19:30

## An FTNC Receiver with +32.5dBm Effective OB-IIP3 Using Baseband IM3 Cancellation

Yudong Zhang, Jianxun Zhu, Peter R. Kinget; Columbia University, USA

**Abstract:** An IM3 cancellation technique is proposed and implemented in a 65nm CMOS 0.5–2.5GHz FTNC (frequency translational noise-cancelling) receiver with a wideband auxiliary path which also offers wideband interferer awareness. It achieves 8.8MHz BB BW, 40dB conversion gain, 3.3dB NF, +5dBm OB-IIP3, and -6.5dBm OB-B1dB without IM3 cancellation while consuming 36mW at 1.2V. Using IM3 cancellation, the equivalent OB-IIP3 for two-tone interferers is up to +32.5dBm with an extra 34mW of power consumption. For two -15dBm modulated interferers 18.8dB cancellation is demonstrated over 10MHz.

#### RSUIF-2 19:30

#### Envelope Time-Domain Characterizations to Assess In-Band Linearity Performances of Pre-Matched MASMOS Power Amplifier

F. Simbélie<sup>1</sup>, V. Gillet<sup>1</sup>, S. Laurent<sup>1</sup>, P. Médrel<sup>1</sup>, Y. Creveuil<sup>2</sup>, M. Régis<sup>2</sup>, M. Prigent<sup>1</sup>, R. Quéré<sup>1</sup>; <sup>1</sup>XLIM, France, <sup>2</sup>ACCO Semiconductor, France

**Abstract:** This paper reports on an innovative in-band linearity performances characterization dedicated to nonlinear RF power amplifiers, here, pre-matched MASMOS power amplifier. It consists of a generic multi-tones test signal that emulates the statistical properties of the applicative signal and allows signal and intermodulation output component separation for in-band C/I (signal to intermodulation power ratio) calculation. Two types of tests are successively discussed. The first one are standards VSA-based measurement performed with a 16-QAM and 256-QAM modulated signal. Secondly, a specific multi-tones signal is presented and compared with the reference VSA measurement. It is shown that the proposed generic stimulus can be used to evaluate, in specific conditions, the in-band interferences that degrade the Error Vector Magnitude (EVM) in the case of a nonlinear link

#### RSUIF-3 19:30

## Improving the Linearity of Wideband Receiver Systems by Component IM3 Phasor Manipulation

Gabor Varga, Fabian Speicher, Arun Ashok, Iyappan Subbiah, Moritz Schrey, Ralf Wunderlich, Stefan Heinen; RWTH Aachen University, Germany

**Abstract:** A linearity improvement technique for receiver systems is presented and verified on a 130nm CMOS high-IF upconverter with 470–790MHz input and 2.4–2.6 GHz output frequency range, enabling WLAN and LTE transceivers to be used as TV White Space Devices. The upconverter reaches a stable IIP $_3$  of 15 dBm, NF of 8 dB and Gain of 7 dB. A linearized LNA and mixer are used as a composite architecture to combine low NF with, even though, high IIP $_3$ . Instead of further maximizing the linearity of the components, the overall performance is optimized on the system level by manipulation and complementary exploitation of the remaining third order intermodulation products of the components.

#### RSUIF-4 19:30

## A Fully-Integrated SOI CMOS Complex-Impedance Detector for Matching Network Tuning in LTE Power Amplifier

D. Nicolas<sup>1</sup>, A. Serhan<sup>1</sup>, A. Giry<sup>1</sup>, T. Parra<sup>2</sup>, E. Mercier<sup>1</sup>; <sup>1</sup>CEA-LETI, France, <sup>2</sup>LAAS, France

**Abstract:** This paper describes a wide dynamic-range and accurate complex-impedance detector for adaptive power amplifier load tuning systems. The detector IC, fabricated in a 130 nm SOI technology, consumes 7 mA under 2.5 V supply voltage. It can handle LTE signals with an input power from 0 dBm up to 40 dBm thanks to its variable attenuator system. System level measurements show that the detector has a very good accuracy in sensing the mismatched load impedance value in the VSWR region from 2:1 to 6:1.

#### RSUIF-5 19:30

## V-Band Flip-Chip pHEMT Balanced Power Amplifier with CPWG-MS-CPWG Topology and CPWG Lange Couplers

Wei-Ling Chang<sup>1</sup>, Jen-Yi Su<sup>1</sup>, Chinchun Meng<sup>1</sup>, Chia-Hung Chang<sup>1</sup>, Guo-Wei Huang<sup>2</sup>; <sup>1</sup>National Chiao Tung University, Taiwan, <sup>2</sup>National Nano Device Laboratories, Taiwan

**Abstract:** A V-band balanced two-stage power amplifier MMICs with Lange couplers is demonstrated using 0.15  $\mu$ m GaAs pHEMT technology in this paper. A CPWG-MS-CPWG topology with via holes at the transistors as the transition between coplanar waveguide with backside ground (CPWG) and microstrip (MS) is employed for the two-stage amplifier. CPWG is applied to realize the flip-chip transition interface for both input and output ports of the amplifier and interstage MS matching has the advantage of small size. The structure parameters of the CPWG Lange coupler and matching network are designed and optimized for power combining. Finally, a 60-GHz balanced two-stage power amplifier using a CPWG-MS-CPWG structure delivers the small signal gain of 18 dB, OP  $_{\rm ldB}$  of 12 dBm and P  $_{\rm sst}$  of 15 dBm.

#### RSUIF-6 19:30

## Multi-Standard 5Gbps to 28.2Gbps Adaptive, Single Voltage SerDes Transceiver with Analog FIR and 2-Tap Unrolled DFE in 28nm CMOS

Mohammad Mahani<sup>1</sup>, Rod Zavari<sup>1</sup>, Su-Tarn Lim<sup>1</sup>, David Hong<sup>1</sup>, Karl Scheffer<sup>1</sup>, Peter Graumann<sup>1</sup>, Hans Ransijn<sup>2</sup>, Tomas Dusatko<sup>3</sup>, Stanley Ho<sup>3</sup>, Philip Snyder<sup>2</sup>, Jomy Joy<sup>4</sup>, Suresh Nalluri<sup>4</sup>, Tony Zortea<sup>2</sup>; <sup>1</sup>Microsemi, Canada, <sup>2</sup>Multiphy, USA, <sup>3</sup>Inphi, Canada, <sup>4</sup>Texas Instruments, India

**Abstract:** A low-power multi-standard transceiver in CMOS 28 nm is presented. The transceiver can be configured to cover the range from 5 Gbps to 28.2 Gbps. Both transmitter and receiver use a supply of 0.92 V. Transmitter uses a 3-tap Finite Impulse Response (FIR) filter and receiver uses a 3-tap analog FIR and 2-tap unrolled Decision Feedback Equalizer (DFE). The entire transceiver uses single level 0.92 V power supply with an analog power consumption of 242.3 mW at 28.2 Gbps. Total area of the transceiver including the Clock Synthesis Unit (CSU) is 0.88 mm².

#### RSUIF-7 19:30

## A Harmonic-Selective Wireless Full-Band-Capture Receiver with Digital Harmonic Rejection Calibration

Hao Wu, David Murphy, Hooman Darabi; Broadcom, USA

**Abstract:** A 30mW Full-Band-Capture receiver based on harmonic selection is presented. The prototype receiver employs a 32-phase non-overlapping LO, and is capable of simultaneously receiving multiple wireless signals arbitrarily located between 600MHz and 3GHz. The receiver achieves 2.4 to 5dB NF and tolerates more than -10dBm out-of-band blockers. A digital harmonic rejection calibration is also proposed to overcome phase and amplitude mismatches in the 32-phase LO and down-conversion paths.

#### **RSUIF-8** 19:30

#### A 40GHz PLL with -92.5dBc/Hz In-Band Phase Noise and 104fs-RMS-Jitter

Ying Chen<sup>1</sup>, Louis Praamsma<sup>1</sup>, Nikola Ivanisevic<sup>2</sup>, Domine M.W. Leenaerts<sup>1</sup>; <sup>1</sup>NXP Semiconductors, The Netherlands, <sup>2</sup>KTH, Sweden

**Abstract:** This paper demonstrates a fully integrated low phase noise PLL at 40GHz, implemented in a 0.25- $\mu$ m SiGe:C BiCMOS technology. An in-band phase noise improvement of 1.4dB to 3.2dB is measured across the locking range using the proposed double-gain PFD. The PLL achieves an in-band phase noise <-92.5dBc/Hz and an integrated RMS jitter of 104fs, a 25% improvement over conventional PFD. The reference spurs are <-73dBc across the whole locking range.

#### RSUIF-9 19:30

## A High-Efficiency Linear Power Amplifier for 28GHz Mobile Communications in 40nm CMOS

Yang Zhang, Patrick Reynaert; Katholieke Universiteit Leuven, Belgium

**Abstract:** This paper presents a high-efficiency, linear power amplifier (PA) for 28GHz mobile communications in 40nm CMOS technology. The design and layout are optimized for high linearity while maintaining high gain and output power. A capacitance neutralized differential pair with source degeneration inductor for linearity enhancement is discussed. The inductive degeneration technique greatly increases the optimal load impedance, which enables a low loss parallel power combining. The complete PA achieves a measured saturated output power of 18.1dBm with 41.5% power-added efficiency (PAE). With 6 Gb/s QAM-64 signals, the proposed PA achieves an average output power of 8.4dBm and 8.8% PAE, with -25 dBc EVM. All measurements are performed with a fixed bias condition

#### RSUIF-10 19:30

#### An Analysis of Phase Noise Requirements for Ultra-Low-Power FSK Radios

Xing Chen, Hun-Seok Kim, David D. Wentzloff; University of Michigan, USA

**Abstract:** This paper presents an analysis of the influence of phase noise (PN) on FSK radios and derives the total PN requirement for a low power FSK link based on Bit Error Rate (BER) performance. A simple noise model is built, including phase noise and white noise from the AWGN channel, to analyze its influence on the BER of an ULP FSK RX. It shows that to achieve a 10<sup>-4</sup> BER, the minimum PN requirement can be more relaxed than current synthesizer designs. The trade-off between PN, data rate, and frequency deviation of FSK modulation is also studied, showing how bandwidth can be traded for relaxed PN while maintaining the same spectral efficiency (bits/Hz). This result implies we could migrate from LC-VCOs to ring oscillators with a simple PLL for wireless communication using FSK and significantly reduce the power of radios. A chip was fabricated to test the accuracy of the model at different PN levels, showing agreement among theoretical analysis, simulations, and measurements.

#### RSUIF-11 19:30

## A Ka-Band 4-Ch Bi-Directional CMOS T/R Chipset for 5G Beamforming System

JangHoon Han, JinHyun Kim, Jeongsoo Park, JeongGeun Kim; Kwangwoon University, Korea

**Abstract:** This paper presents a Ka-band 4-channel bi-directional T/R chipset in 65 nm CMOS technology for 5G beamforming system. The proposed T/R chipset can provide bi-directional operation with moderate gain and dual polarization. Each channel consists of bi-directional gain blocks, a 5-bit step attenuator and a 5-bit phase shifter including tuning bits. The phase and attenuation coverage are 348° with the LSB of 11.25° and 31 dB with the LSB of 1 dB, respectively. The gain of 13 dB (Tx mode) and 6 dB (Rx mode) are achieved at 28 GHz including the 4-way power divider/combiner.

#### RSUIF-12 19:30

## A 32GHz 20dBm-P<sub>SAT</sub> Transformer-Based Doherty Power Amplifier for Multi-Gb/s 5G Applications in 28nm Bulk CMOS

Paramartha Indirayanti, Patrick Reynaert; Katholieke Universiteit Leuven, Belgium

**Abstract:** This paper presents a 32 GHz transformer-based Doherty power amplifier (PA) in a 28 nm bulk CMOS process. There are two techniques proposed: linearization by means of AM-PM and AM-AM compensation of the class AB and the class C amplifiers; and parallel-series-parallel power power combiner, wherein a current-mode parallel combiner complements the Doherty's voltage-mode series combiner to boost the output power. A saturated output power ( $P_{SAT}$ ) of 19.8 dBm and an OP1dB of 16 dBm are accomplished from 1V supply while supporting 15 Gb/s 64-QAM amplification at 11.7 dBm average output power. The chip achieves 21% PAE at  $P_{SAT}$  and occupies 0.59 mm² active area.

#### RSUIF-13 19:30

## A 10–40GHz Frequency Quadrupler Source with Switchable Bandpass Filters and >30dBc Harmonic Rejection

Hyunchul Chung, Qian Ma, Gabriel M. Rebeiz; University of California, San Diego, USA

**Abstract:** This paper presents a 10–40 GHz wideband frequency quadrupler in GF8HP 0.13  $\mu m$  SiGe BiCMOS process. Three bands (low-, mid-, and high-band) are implemented on-chip for wideband operation. An on-chip 4-pole switchable elliptic bandpass filter is also used to result in greatly improved harmonic rejection ratio (HRR). The measured worstcase HRR is 32–48 dBc at 11–40 GHz with an output power of +1 to -8 dBm for  $P_{\rm in}$  = 1 dBm (25–32 dB at 10–11 GHz). The output power and HRR remain nearly constant with  $P_{\rm in}$  of 0–7 dBm. The chip is 3.96 mm² and consumes 60 mW in low- and mid-band modes, and 84 mW for the high-band mode. To our knowledge, this wideband frequency quadrupler represents state-of-the-art performance in terms of bandwidth, HRR and  $P_{\rm out}$ . Application areas are wideband low-harmonic content sources for wideband measurement systems, high-resolution imaging systems and digital beamforming phased-arrays.

#### RSUIF-14 19:30

## Joint TX and Feedback RX IQ Mismatch Compensation for Integrated Direct Conversion Transmitters

Hunsoo Choo, Charles Sestok, Xiaoxi Zhang, Nikolaus Klemmer; Texas Instruments, USA

**Abstract:** The direct conversion (DC) architecture has been adopted for wireless base-station transceivers due to its cost and area efficiency. The shortcomings of DC transceivers need to be overcome to meet their high performance requirements. In-phase (I) and quadrature phase (Q) mismatch is one of most significant impairments. This paper presents an integrated, on-line mismatch compensation system which calibrates frequency-dependent transmitter (TX) and feedback receiver (FBRX) IQ mismatches using the digital TX signal as a reference. The proposed method was fabricated in 45nm CMOS technology. Measurements show 60 dBc TX ACPR for 20MHz LTE low-IF signals. TX EVM of 0.8% is achieved with 20MHz zero-IF LTE signals.

#### RSUIF-15 19:30

## A Precision 140MHz Relaxation Oscillator in 40nm CMOS with 28ppm/°C Frequency Stability for Automotive SoC Applications

Dmytro Cherniak, Roberto Nonis, Fabio Padovan; Infineon Technologies, Austria

**Abstract:** The need for high-frequency, low-power, wide temperature range, precision on-chip reference clock generation makes relaxation oscillator topology an attractive solution for various automotive applications. This paper presents for the first time a 140MHz relaxation oscillator with robust-against-process-variation temperature compensation scheme. The high-frequency relaxation oscillator achieves 28 ppm/°C frequency stability over the automotive temperature range from -40 to 175°C. The circuit is fabricated in 40nm CMOS technology, occupies 0.009mm² and consumes  $294\mu W$  from 1.2V supply.

#### Monday 5th June 2017 08:00-09:20 HCC Room 312

#### Session RMO1A: 28GHz Phased-Array Transceivers for 5G Systems

Chair: Stefano Pellerano, Intel Corporation

Co-Chair: Hossein Hashemi, University of Southern California

#### RMO1A-1 08:00

## Bi-Directional Flip-Chip 28GHz Phased-Array Core-Chip in 45nm CMOS SOI for High-Efficiency High-Linearity 5G Systems

Umut Kodak, Gabriel M. Rebeiz; University of California, San Diego, USA

**Abstract:** This paper presents a 0 mW two-channel 28 GHz bi-directional phased-array chip packaged using flip-chip interconnects in 45nm CMOS SOI. The design alternates switched-LC phase shifters with switched attenuators to result in 5-bit phase control with an rms gain and phase error <0.8 dB and 5°, respectively at 25–33 GHz. In the RX mode, the measured gain is -10 dB and the NF is 10 dB with an input  $P_{1dB}$  of 5 dBm. In the TX mode, the measured output  $P_{1dB}$  is -2 dBm. This work presents an efficient solution for the construction of high-linearity and high-power phased-array base-stations by combining GaAs front-ends with a passive silicon core chip.

#### RMO1A-2 08:20

## A 28-GHz Phased-Array Transceiver with Series-Fed Dual-Vector Distributed Beamforming

Yi-Shin Yeh¹, Ed Balboni², Brian Floyd¹; ¹North Carolina State University, USA, ²Analog Devices, USA **Abstract:** This paper presents a 28-GHz four-element phased-array transceiver in 130-nm SiGe BiCMOS technology for 5G cellular application. The array employs scalar-only weighting functions within each front-end and a global quadrature function, enabling small footprint for each element. A dual-vector series feed network also reduces size of the array. Measurements show that each receive front-end achieves 8.7 to 11.5 dB gain, 4.5 to 6.9 dB noise figure, -25.4 to -18.4 dBm input 1-dB compression point, and < 0.5dB/2.1° RMS gain/phase error at 24 to 28 GHz. Each transmit front-end achieves 9.4 to 14.3 dB gain, 5.5 to 10.6 dBm output 1-dB compression point, and < 0.4dB/4.2° RMS gain/phase error at 24 to 28 GHz. The four-element transceiver array occupies 2.9 mm² area and consumes 1.08 W in transmit mode and 0.68 W in receive mode.

#### RMO1A-3 08:40

#### A 28GHz CMOS Direct Conversion Transceiver with Packaged Antenna Arrays for 5G Cellular System

Hong-Teuk Kim, Byoung-Sun Park, Seung-Min Oh, Seong-Sik Song, Jong-Moon Kim, So-Hyeong Kim, Tak-Su Moon, Seung-Yeon Kim, Ji-Young Chang, Sung-Woong Kim, Woo-Seong Kang, Seung-Yoon Jung, Geum-Young Tak, Jin-Kyoung Du, Yu-Suhk Suh, Yo-Chuol Ho; LG Electronics, Korea

**Abstract:** This paper describes a 28GHz CMOS direct conversion transceiver with packaged  $2\times4$  patch antenna arrays for 5G communication. Test results show good RF performances of Rx NF 6.7dB, Maximum Tx EIRP 31.5dBm (1PA  $P_{out\_sat} = 10.5dBm$ ), LO integrated phase noise -37.8dBc  $(0.67^{\circ})$ , Rx/Tx EVM around 2.2% (-33.1dB) at mid RF power, and well-fitted beam control capability.

#### RMO1A-4 09:00

## An Ultra Low-Cost 32-Element 28GHz Phased-Array Transceiver with 41dBm EIRP and 1.0–1.6Gbps 16-QAM Link at 300 Meters

Kerim Kibaroglu, Mustafa Sayginer, Gabriel M. Rebeiz; University of California, San Diego, USA **Abstract:** This paper presents a 32-element phased-array architecture suitable for fifth-generation (5G) communication links. A 28–32 GHz silicon core chip is designed with 4 transmit/receive elements each with 14 dB gain control, 6-bit phase control, 4.6 dB measured noise figure (NF) in the RX mode and 10 dBm output 1 dB compression point (OP1dB) in the TX mode. Eight of these chips are flipped on a low-cost printed circuit board (PCB) with integrated antennas and Wilkinson combiners. The 32-element array has a measured EIRP of 41 dBm at P1dB, can scan to  $\pm 20^{\circ}$  and  $\pm 50^{\circ}$  in E- and H-planes, and consumes 4.2 W and 6.4 W in RX and TX modes, respectively. The array is used in a 300 meter wireless link and achieves a data rate of 1.0–1.6 Gbps at 16-QAM for all scan angles with <12% EVM. To our knowledge, this represents state-of-the art in 28 GHz phased-arrays in terms of chip performance and integration level.

#### Monday 5th June 2017 08:00-09:20 HCC Room 313A

## Session RMO1B: Advanced Technologies for Optical, Millimeter-Wave and Radio Frequency Applications

Chair: Freek van Straten, Ampleon Co-Chair: Richard Chan, QORVO

#### RMO1B-1 08:00

## Sub-THz Source Integrated in Low-Cost Silicon Photonic Technology Targeting 40Gb/s Wireless Links

Elsa Lacombe<sup>1</sup>, Frederic Gianesello<sup>1</sup>, Cedric Durand<sup>1</sup>, Guillaume Ducournau<sup>2</sup>, Cyril Luxey<sup>3</sup>, Daniel Gloria<sup>1</sup>; <sup>1</sup>STMicroelectronics, France, <sup>2</sup>IEMN, France, <sup>3</sup>EpOC-UNS, France

**Abstract:** Following the race for transmitting/receiving at higher data rate, we can observe intensive development of millimeter-wave wireless systems in low-cost CMOS technology. Data rates above 10 Gb/s are now targeted in order to address the data traffic bottleneck of backhaul links for the 5G wireless network. To do so, antenna-systems operating at sub-THz frequencies show great potential, leveraging high-performance photonic technology. This paper presents a sub-THz source based on a SiGe PIN photodiode integrated in low-cost Silicon Photonic technology. Using a laser beat-note, the photodiode delivers an output power ranging from -20 dBm to -29 dBm between 125 and 325 GHz. Leveraging this wide operating band, data rate exceeding 40 Gb/s can be targeted.

#### RMO1B-2 08:20

#### RF NMOS Switch with Dedicated Sinks for Reduced Leakage Current

M.S.M. Al-Sa'di, J.J.T.M. Donkers, P.H.C. Magnée, I. Brunets, J.W. Slotboom; NXP Semiconductors, The Netherlands

**Abstract:** In this paper we introduce a method to significantly reduce the substrate leakage current in an RF NMOS switch device without degrading the device figure-of-merit ( $R_{on} \times C_{off}$ ), and with no increase in device complexity. This is based on modifying the structure layout, and introducing dedicated sinks. These sinks prevent the substrate's minority carriers from reaching the source/drain regions, thereby removing it from the signal path. In addition, this approach allows independent tuning of two parameters, leakage and  $R_{oo} \times C_{off}$  figure-of-merit.

#### RMO1B-3 08:40

#### RF-pFET in Fully Depleted SOI Demonstrates 420GHz F<sub>T</sub>

Josef Watts<sup>1</sup>, Kumaran Sundaram<sup>2</sup>, Kok Wai Johnny Chew<sup>2</sup>, Steffen Lehmann<sup>3</sup>, Shih Ni Ong<sup>2</sup>, Wai Heng Chow<sup>2</sup>, Lye Hock Chan<sup>2</sup>, Jerome Mazurier<sup>4</sup>, Christoph Schwan<sup>3</sup>, Yogadissen Andee<sup>4</sup>, Thomas Feudel<sup>3</sup>, Luca Pirro<sup>4</sup>, Elke Erben<sup>3</sup>, Edward Nowak<sup>1</sup>, Elliot Smith<sup>3</sup>, El Mehdi Bazizi<sup>3</sup>, Thorsten Kammler<sup>3</sup>, Richard Taylor III<sup>1</sup>, Bryan Rice<sup>3</sup>, David Harame<sup>3</sup>; <sup>1</sup>GLOBALFOUNDRIES, USA, <sup>2</sup>GLOBALFOUNDRIES, Singapore, <sup>3</sup>GLOBALFOUNDRIES, Germany, <sup>4</sup>CEA-LETI, France

**Abstract:** We report an experimental pFET with 420GHz  $f_{\gamma\gamma}$ , which to the best of our knowledge is the highest value reported for a silicon pFET. The transconductance is  $1800\mu S/\mu m$ . The technology is fully depleted silicon on insulator (FDSOI) with the pFET channel formed by SiGe condensation. This outstanding performance is achieved by a combination of layout and process optimization which minimizes capacitance and maximizes compressive strain on the channel. The technology features a high-k metal gate and short gate length (20nm drawn) in addition to the SiGe channel for high mobility.

#### RMO1B-4 09:00

## Validation of a Functional Principle for a Broadband Millimeter-Wave Power Detection Structure in a Recent BiCMOS Technology

F. Trenz<sup>1</sup>, R. Weigel<sup>1</sup>, Dietmar Kissinger<sup>2</sup>; <sup>1</sup>FAU Erlangen-Nürnberg, Germany, <sup>2</sup>IHP, Germany

**Abstract:** In this paper, a functional principle for a broadband thermal detector suited for a monolithical integration is shown. Two tantalum load resistors are heated by an input signal, while the temperature at a fixed distance is recorded on chip with a differential temperature sensing bridge. An integrated differential to single-ended stage amplifies the bridges differential voltage and provides an output voltage proportional to the input power of the detector. The thermal resistance and capacitance between the load resistor and the sensing cell act as a low pass filter in the electrical regime. Based on this concept, a detector chip has been designed, which has been analyzed in thermal simulations. The realized detector has been characterized on-chip and bonded to a microwave substrate for a system performance estimation. Its input impedance is tuned to 50 Ohms and measured matching is better than -15 dB from 150MHz to 110GHz. With a low supply voltage of 1.5V and its active area of around  $80\times36\mu\text{m}^2$ , the detector is suitable for an integrated power measurement solution.

#### Monday 5th June 2017 08:00-09:40 HCC Room 313B

#### **Session RMO1D: High-Performance Frequency Synthesizers**

Chair: Jeyanandh Paramesh, Carnegie Mellon University Co-Chair: Jaber Khoja, Rockwell Collins

#### RMO1D-1 08:00

#### A 59-to-276GHz CMOS Signal Generation for Rotational Spectroscopy

Xiaolong Liu<sup>1</sup>, Yue Chao<sup>2</sup>, Howard C. Luong<sup>1</sup>; <sup>1</sup>HKUST, China, <sup>2</sup>Qualcomm, USA

**Abstract:** An ultra-wideband sub-THz signal generation system is proposed for rotational spectroscopy employing a magnetic-tuning varactor-less quad-band voltage-controlled oscillator (QB-VCO), a locking-range-enhanced dual-mode injection-locked frequency divider (DM-ILFD), a power-efficient injection-locked oscillator (ILO) as a driver, and sub-THz mixers with frequency multipliers for frequency extension. Implemented in a 65-nm CMOS process and consuming 54 mW, the prototype measures an ultra-wide frequency tuning range from 58.8 to 275.6 GHz with 10-MHz offset phase noise from -115.8 dBc/Hz to -89.2 dBc/Hz while occupying a core area of 0.9 mm  $\times$  0.72 mm.

#### RMO1D-2 08:20

# A Fully Integrated 75–83GHz FMCW Synthesizer for Automotive Radar Applications with -97dBc/Hz Phase Noise at 1MHz Offset and 100GHz/mSec Maximal Chirp Rate

Jakob Vovnoboy, Run Levinger, Nadav Mazor, Danny Elad; ON Semiconductor, Israel

**Abstract:** We present a SiGe BiCMOS fully integrated 75–83 GHz FMCW synthesizer for automotive radar applications. Performance enhancements were achieved by utilizing the bulk-drain parasitic variable capacitance of P-channel transistors, embedded in a gm-boosted Colpitts VCO, for frequency control. This mechanism was incorporated in a dual path PLL, providing low loop bandwidth variation over the whole output frequency range, -97 dBc/Hz phase noise at 1 MHz offset and maximum chirp rate of 100 GHz/mSec.

#### RMO1D-3 08:40

## A Subharmonically Injection-Locked PLL with 130fs RMS Jitter at 24GHz Using Synchronous Reference Pulse Injection from Nonlinear VCO Envelope Feedback

Dongseok Shin, Shinwoong Park, Sanjay Raman, Kwang-Jin Koh; Virginia Tech, USA

**Abstract:** This paper presents an 8 GHz subharmonically injection-locked PLL (SILPLL), which is cascaded with a 24 GHz quadrature injection-locked oscillator in 130 nm CMOS. The proposed SILPLL adopts an envelope-detection based injection-timing calibration for synchronous reference

pulse injection to a VCO. With one of the largest frequency division ratios (N=80) reported so far, the SILPLL exhibits 124 fs and 130 fs RMS jitter at 8 GHz and 24 GHz, respectively, with <-49 dBc reference spur. The measured phase noise at 1 MHz offset is -114 dBc/Hz at 8 GHz and -104 dBc/Hz at 24 GHz.

#### RMO1D-4 09:00

## A Highly Reconfigurable RF-DPLL Phase Modulator for Polar Transmitters in Multi-Band/Multi-Standard Cellular RFICs

T. Buckel<sup>1</sup>, T. Mayer<sup>2</sup>, T. Bauernfeind<sup>2</sup>, S. Tertinek<sup>2</sup>, C. Wicpalek<sup>2</sup>, A. Springer<sup>1</sup>, R. Weigel<sup>3</sup>, T. Ussmueller<sup>4</sup>; <sup>1</sup>Johannes Kepler Universität Linz, Austria, <sup>2</sup>DMCE, Austria, <sup>3</sup>FAU Erlangen-Nürnberg, Germany, <sup>4</sup>Universität Innsbruck, Austria

**Abstract:** A multirate, fractional-N RF digital phase-locked loop (DPLL) phase modulator implementation for polar transmitter supporting cellular communication standards up to 4G LTE-A is demonstrated for the first time. The RF-DPLL integrates LC-tank-based digital-controlled oscillator (DCO) cores with  $\Sigma\Delta$ -noise shaping and fractional sample rate conversion to account for a broad range of frequency bands and spectral emission requirements. A two-point modulation with different sampling rates and signal scaling is applied to optimize the system for operation in narrow-band and wide-band phase modulation. DCO predistortion and DCO gain estimation is implemented to achieve sufficiently low in-band distortion. Measurement results of the RF-DPLL system as part of a polar transmitter implemented in 28-nm CMOS are shown, fulfilling 3GPP specifications for LTE-A uplink.

#### RMO1D-5 09:20

## A Low-Noise Inductor-Less Fractional-N Sub-Sampling PLL with Multi-Ring Oscillator

Dongyi Liao, Ruixin Wang, Fa Foster Dai; Auburn University, USA

**Abstract:** In this paper, a compact inductor-less PLL using multiple coupled rings oscillator is presented. Sub-sampling technique with soft loop gain switching is applied to reduce the in-band phase noise. As a result, the loop bandwidth can be widened, which suppresses the phase noise from ring oscillator as well. Fractional-N mode is implemented by utilizing the multiple phase outputs inherently generated by the ring VCO. Using multiple rings instead of one allows generating more phases for finer frequency resolution without decreasing oscillation frequency. The coupled multiring oscillator with proper phase shift also achieves reduced phase noise comparing to their single-ring counterpart. The PLL was implemented in a 0.13μm CMOS technology, consuming 19 mW from a 1.3 V power supply. The measured largest in-band fractional spur at 2.08 MHz is -42 dBc. The measured integrated jitters were 571 fs and 690 fs around 1.2GHz output in integer mode and fractional mode respectively, achieving a FoM of -230 dB.

#### Monday 5th June 2017 10:00-11:20 HCC Room 312

#### Session RMO2A: Radio Building Blocks for 5G Systems

Chair: Walid Ali-Ahmad, Qualcomm

Co-Chair: Bodhisatwa Sadhu, IBM T.J. Watson Research Center

#### RMO2A-1 10:00

## A 25–30GHz 8-Antenna 2-Stream Hybrid Beamforming Receiver for MIMO Communication

Susnata Mondal, Rahul Singh, Ahmed I. Hussein, Jeyanandh Paramesh; Carnegie Mellon University, USA

**Abstract:** This paper presents a 65 nm CMOS 25–30 GHz hybrid beamforming receiver with eight antenna inputs and two baseband output streams. The receiver uses the Cartesian-Combining architecture, which is introduced for two baseband streams. Each antenna signal is complex-weighted independently and combined with weighted signals from other antennas prior to downconversion. Each RF-domain complex weight is realized using a pair of 5-bit digitally controlled VGA's. The receiver achieves 34 dB conversion gain, 7.3 dB minimum noise figure, and 5 GHz of RF bandwidth while consuming only 27.5 mW power per antenna element (340 mW for the entire receiver). Two-element Cartesian-combining achieves a peak-to-null ratio of 20 dB. Use of mostly active phase shifting and combining approach made the design ultra-compact with 3.86 mm² core area for entire 8-element 2-stream receiver.

#### RMO2A-2 10:20

## A 29-to-57GHz AM-PM Compensated Class-AB Power Amplifier for 5G Phased Arrays in 0.9V 28nm Bulk CMOS

Marco Vigilante, Patrick Reynaert; Katholieke Universiteit Leuven, Belgium

**Abstract:** This paper presents a 29-to-57GHz (65% BW) AM-PM compensated class-AB power amplifier tailored for 5G phased arrays. Designed in 0.9V 28nm CMOS without RF thick top metal, the PA achieves a  $P_{sat}$ =15.1dBm±1.6dB and |AM-PM|<1° from 29-to-57GHz, with a peak PAE of 24.2%. Techniques are studied to realize the required load impedance and distortion cancellation over the wide band of operation, while allowing 2-way power combining to further increase the delivered POUT. The very low AM-PM distortion of the realized PA enables up to 10.1, 8.9, 5.9dBm average  $P_{OUT}$  while amplifying a 1.5, 3, 6Gb/s 64-QAM respectively at 34GHz with EVM/ACPR better than -25dBc/-30dBc, without any digital pre-distortion.

#### RMO2A-3 10:40

## A Quad Channel 11-bit 1GS/s 40mW Collaborative ADC Based Enabling Digital Beamforming for 5G Wireless

Aurangozeb¹, Farshid Aryanfar², Masum Hossain¹, ¹University of Alberta, Canada, ²Straight Path Communications, USA

**Abstract:** A  $4 \times 11$ -bit 1 GS/s 40 mW Collaborative ADC in 65nm CMOS is presented for a 4-Ch MIMO receiver. It utilizes the correlation information between channels to perform energy efficient digitization of received signals. By utilizing 8 SAR units each with 6-bit level of resolution, four level of ADC resolutions (11, 9, 6, and 6-bit), is achieved dynamically for optimal performance. This collaborative ADC in compare to all-11 and all-9 bit has an area and power reduction of 50% and 41% respectively with only 10% degradation in overall SNDR.

#### RMO2A-4 11:00

## A 16-Element 4-Beam 1GHz-IF 100MHz-Bandwidth Interleaved Bit-Stream Digital Beamformer in 40nm CMOS

Sunmin Jang<sup>1</sup>, Jaehun Jeong<sup>2</sup>, Rundao Lu<sup>1</sup>, Michael P. Flynn<sup>1</sup>; <sup>1</sup>University of Michigan, USA, <sup>2</sup>Broadcom, USA

**Abstract:** This paper introduces a 16 element, 1GHz IF input, digital beamformer (DBF) that generates 4 independent simultaneous beams, with 100MHz bandwidth. Although DBF has several advantages over analog beamforming, including higher accuracy and multiple beam generation, application of on-chip DBF has been limited due to high power consumption and large die area. The proposed architecture addresses these issues by combining efficient Continuous-Time Band-Pass Delta Sigma Modulators (CTBPDSMs) with Interleaved Bit-Stream Processing (IL-BSP). IL-BSP saves 80% power and 80% area compared to a conventional DSP approach. The overall 16 element array has a measured 58.5dB SNDR and a 59.6dB SNR over a 100MHz bandwidth (11.2dB array gain). Thanks to the IL-BSP approach, the measured beam patterns are near ideal.

#### Monday 5th June 2017 10:00-11:40 HCC Room 313A

#### Session RMO2B: Modeling and Characterization for Emerging High Frequency and RF Front-End Applications

Chair: Tzung-Yin Lee, Skyworks Solutions Co-Chair: Edward Preisler, TowerJazz

#### RMO2B-1 10:00

## Accurate Modelling and Optimization of Inhomogeneous Substrate Related Losses in SPDT Switch IC Design for WLAN Applications

Fadoua Gacim, Philippe Descamps; CRISMAT, France

**Abstract:** This paper teaches the way to achieve an optimum substrate isolation in RF switch design thanks to Deep Trenches Isolation (DTI). The role of Deep Trench Isolation in substrate coupling around active blocks is analysed in link to its ability to break the conductive buried layers in the substrate. Then, an accurate modelling approach based on quasi-static approach developed for inhomogeneous substrate is investigated. The efficiency of this methodology is first demonstrated thanks to a comparison with a standard numerical method based on FEM (Finite Element Method). Then, experiments data are provided to support this theoretical analysis. The methodology is fully integrated in a commercial design flow and offers a perfect trade-off between accuracy and run time simulation. From available test data on single device and a full SP3T, a correlation better than 0.1dB is obtained between simulation and measurement up to 8 GHz.

#### RMO2B-2 10:20

#### A Simplified CMOS FET Model Using Surface Potential Equations for Inter-Modulation Simulations of Passive-Mixer-Like Circuits

Mahmood Baraani Dastjerdi, Harish Krishnaswamy; Columbia University, USA

**Abstract:** In many CMOS analog/RF circuits, such as passive mixers or N-path filters, the transistor operates as a switch. Switching circuits often experience source-drain reversal, and most transistor models exhibit discontinuities in second and higher-order derivatives of the drain current around zero drain-source bias. This introduces fundamental challenges in performing third-order intermodulation distortion simulations. In this work, a method is presented to replace the factory models with equivalent surface potential models for static current in conjunction with a simple circuit to take into account second-order parasitics, namely, gate current and terminal capacitors. The modeling approach may be utilized even if device measurements are not available, is shown to be simultaneously more computationally efficient and accurate than prior approaches, and is validated through measurements from a 0.15–2.5GHz mixer-first receiver in 65nm CMOS that exhibits +34.8dBm out-of-band IIP3.

#### RMO2B-3 10:40

## Broadband Effect of Linear Tapered Transitions Between Probe Pads and GCPW Signal Lines On-Chip

Tinus Stander; University of Pretoria, South Africa

**Abstract:** To effect a low-reflection interconnect between GSG probe pads and on-chip GCPW, a linear taper between the signal pad and the GCPW signal line is often included. This work evaluates, both in parametric simulation and experimentation, the effect of this taper shape to the input reflection in the band 1–110 GHz. It is found that, although longer tapers offer some advantage below 30 GHz, the taper ultimately impedes the input reflection of the interconnect.

#### RMO2B-4 11:00

#### Accurate EM Simulation of SMT Components in RF Designs

Weimin Sun; Skyworks Solutions, USA

**Abstract:** SMD is designed into many MCM/SiP products, but accurate EM simulation of SMD in a design has been a challenge. In fact, circuit simulation with an EM MCM model connected with vendor-provided SMT models often leads to a shift of harmonic trap notch. Such shift may be attributed to the intrinsic inductance of an EM port. In this paper, we focus on EM models of HFSS, present discovery of intrinsic port inductance in an HFSS model and discuss issues and techniques on how to handle lumped SMT ports in an HFSS EM model for more accurate SMD circuit simulation.

#### RM02B-5 11:20

## Variation of Intrinsic Components from Small-Signal Model of AlGaN/GaN HEMTs in Linear and Saturation Regions After Off-State Bias

Yue-ming Hsin, Yi-Nan Zhong, Zhen-Wei Liu; National Central University, Taiwan

**Abstract:** Current dispersion is an issue in AlGaN/GaN HEMTs. Different methods have been reported to investigate this phenomenon. This study reports an investigation of intrinsic components from small-signal model of AlGaN/GaN HEMTs right after off-state bias in linear and saturation regions in addition to drain-lag measurement. Different variations on the intrinsic components after off-state bias in linear and saturation regions were observed after switching from off-state bias. A significant current dispersion from drain-lag measurement is related to the increase in  $R_{\rm ds}$  and decrease in  $C_{\rm ds}$  extracted from small-signal model. However, less changes in  $C_{\rm es}$  and  $C_{\rm ed}$  were observed.

#### Monday 5th June 2017 10:00-11:40 HCC Room 313B

#### Session RMO2D: Millimeter-Wave and THz Sources

Chair: Mohyee Mikhemar, Broadcom Co-Chair: Ehsan Afshari, University of Michigan

#### RMO2D-1 10:00

## An 8-Element Common-Mode-Coupled 106GHz Fundamental Oscillator with -111 dBc/Hz Phase Noise at 1MHz Offset

Alireza Imani, Hossein Hashemi; University of Southern California, USA

**Abstract:** Phase noise reduces in a coupled array of oscillators at an ideal rate of 3N dB for 2<sup>N</sup> oscillators. Concept of "common-mode coupling" is introduced as a robust technique in reducing phase noise in mm-wave frequencies. A 106 GHz 8-element common-mode coupled Colpitts oscillator is implemented in a 130 nm SiGe HBT BiCMOS technology with a measured phase noise of -111 dBc/Hz at 1 MHz offset while consuming 90 mW. The core differential Colpitts oscillator uses a resonant biasing scheme to reduce phase noise. The improvement of phase noise compared to the stand-alone oscillator is 9 dB showing the effectiveness of the proposed coupling scheme.

#### RMO2D-2 10:20

# A 195GHz Single-Transistor Fundamental VCO with 15.3% DC-to-RF Efficiency, 4.5mW Output Power, Phase Noise FoM of -197dBc/Hz and 1.1% Tuning Range in a 55nm SiGe Process

Hamid Khatibi¹, Somayeh Khiyabani¹, Andreia Cathelin², Ehsan Afshari³; ¹Cornell University, USA, ²STMicroelectronics, France, ³University of Michigan, USA

**Abstract:** A novel approach to design efficient high-output-power fundamental oscillators close to the  $f_{max}$  of the employed process is presented. The idea is based on shaping and optimizing the maximally efficient power gain  $(G_{ME})$  of the circuit using a pair of internal/external feedback mechanisms. Solving a constrained optimization problem, an optimum pair of passive feedback network is designed to achieve the highest maximally efficient power gain in order to increase the output power and thence the DC-to-RF efficiency. A 195 GHz fundamental oscillator is designed in a 55 nm SiGe process  $(f_{max} \cong 340 \text{GHz})$ , which achieves a significantly higher DC-to-RF efficiency (15.3%) among all reported oscillators working above  $f_{max}/3$  of their active devices. The oscillator generates a peak power of 4.5 mW (6.5 dBm) with the best phase noise of -82.3 dBc/Hz and the best FoM of -197 dBc/Hz measured at 100 KHz offset frequency, which is the best phase noise and FoM among all CMOS/SiGe mm-Wave oscillators. The proposed optimization-based method takes into account PVT variations as well as modeling errors of all components in the design process to guarantee the functionality of the fabricated circuit.

#### RMO2D-3 10:40